コンパレータの設計方法とヒステリシスの作り方

コンパレータとは、2つの入力電圧を比較して出力を切り替える回路です。

非反転入力端子(+端子)の電圧の方が高ければ出力電圧はHi、反転入力端子(-端子)の電圧の方が高ければ出力電圧はLoとなります。

片側の入力電圧を固定して閾値とし、もう一方の電圧が閾値より高いか低いかを判定する回路として使われることが多いです。

本稿では、コンパレータの使い方と、トランジスタレベルでの設計方法について解説していきます。

コンパレータの動作原理

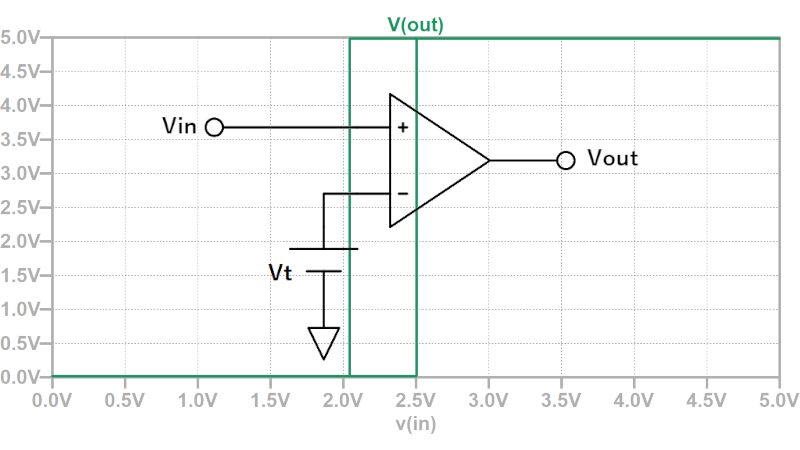

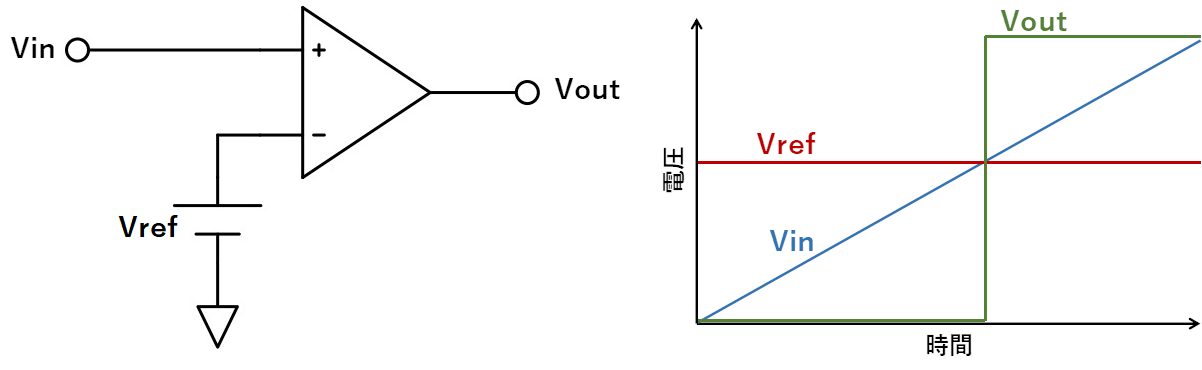

コンパレータの回路記号は、オペアンプと同じで2つの入力端子と出力端子で描かれます。

冒頭でも説明しましたが、よく使われる例として、反転入力端子を固定電圧、非反転入力端子電圧をスイープした場合の動作を図示します。

Vin<Vrefの状態では出力電圧はLo、Vin>Voutとなると出力電圧はHiに遷移します。

したがって、Vinの電圧がVrefより高いか低いかを判定することができます。

Hiレベルは通常コンパレータの電源電圧であり、LoレベルはGNDになります。

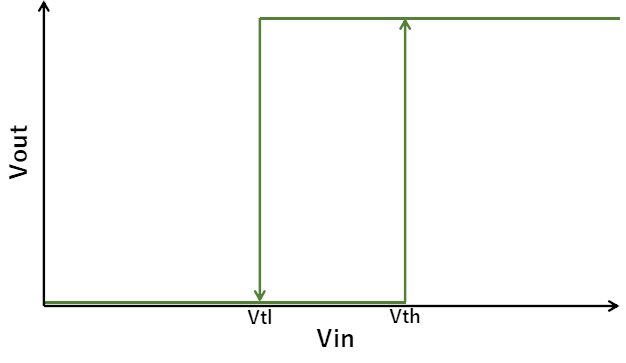

ヒステリシスが必要な理由

通常、コンパレータにはヒステリシスが設定されています。

コンパレータの場合、入力が低い側から高い側へ遷移するときの閾値と、高い側から低い側へ遷移するときの閾値が変わります。

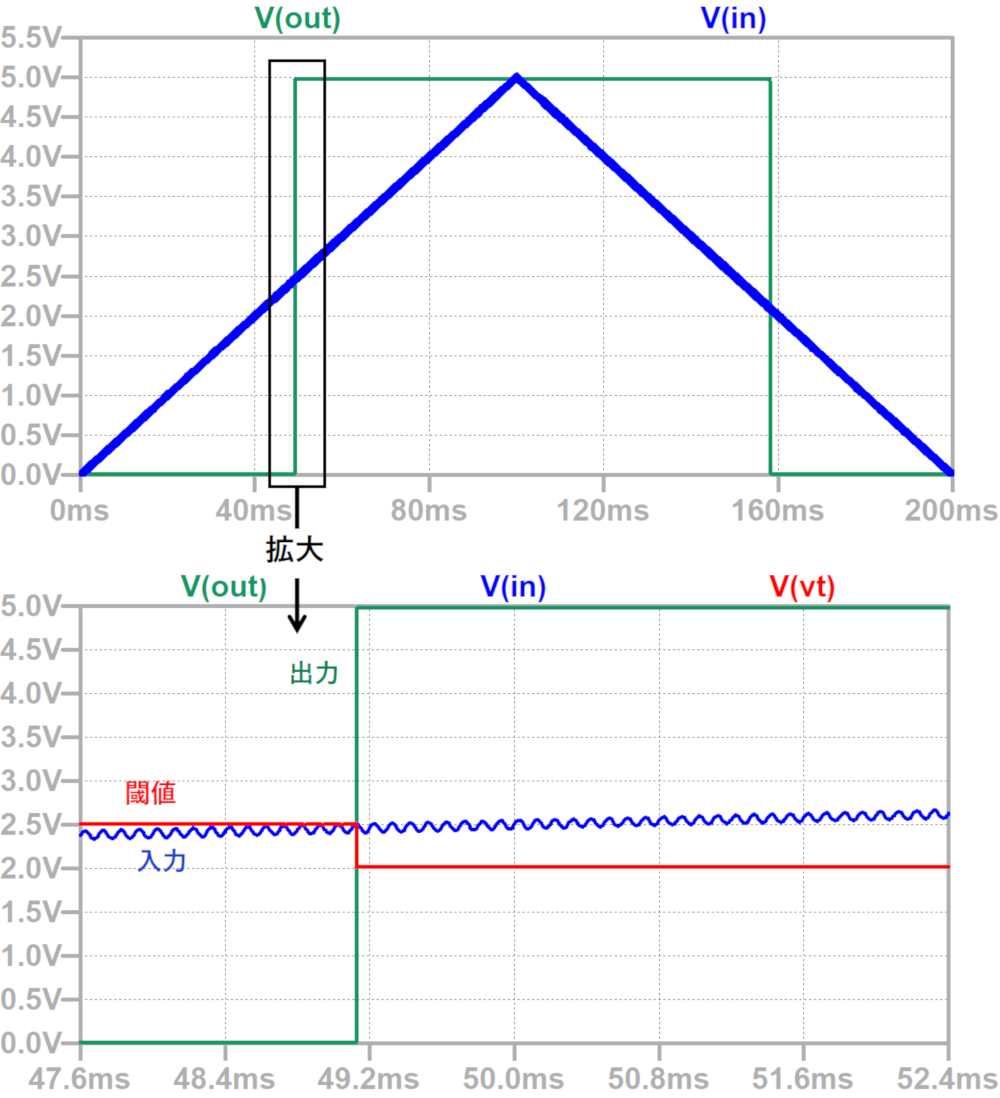

ヒステリシスがない場合、出力にチャタリングが発生する場合があります。

入力信号にノイズが重畳している場合、ノイズによって閾値を行ったり来たりするために起こります。

ヒステリシスがあると、入力が閾値を超えた瞬間に閾値を引き下げるためチャタリングが起こりません。

コンパレータの内部回路

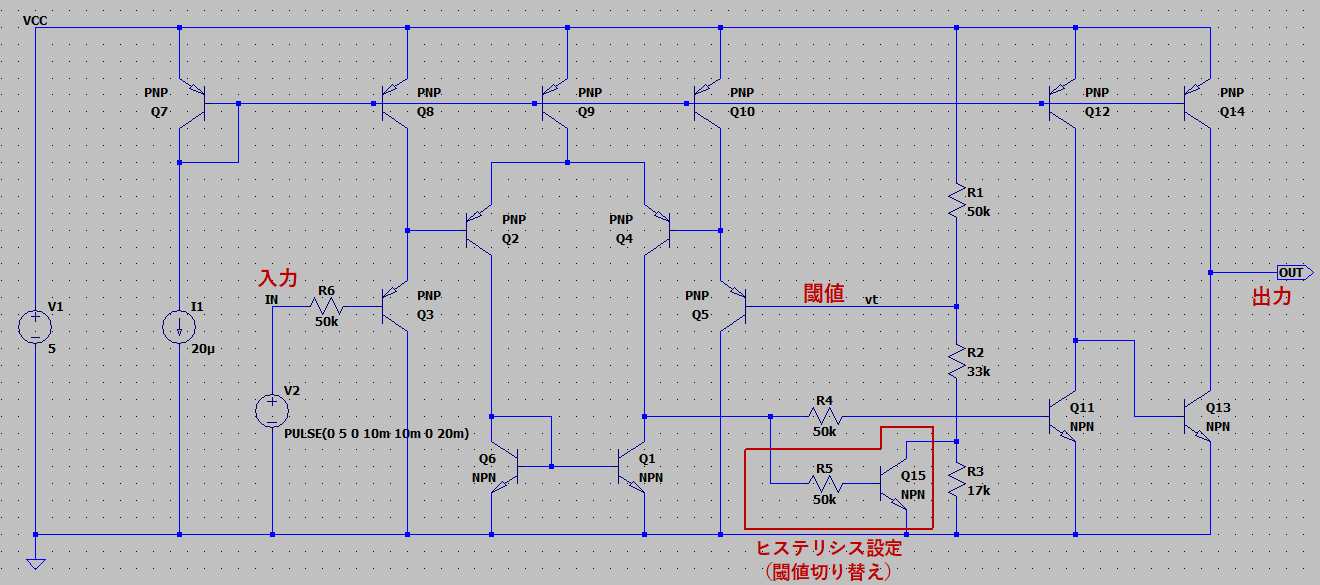

コンパレータをトランジスタレベルで設計した場合の回路図を示します。

コンパレータは差動増幅回路(差動対)とエミッタ接地回路で構成されます。

エミッタ接地によりゲインを上げて切り替わりを急峻にし、さらにHiレベルのレベルシフトを行います。

コンパレータの閾値は差動対の右側入力に接続されている抵抗:R1~R3の抵抗分割で決められています。

R3にはトランジスタが接続されていて、オンすることでR3がショートされて閾値が低くなります。

これによりヒステリシスを生成しています。

設計計算

閾値の設計計算を行います。

R1=50kΩ、R2=33kΩ、R3=17kΩとしています。

Vin<Vtの状態では、差動対の出力がLoとなるためトランジスタ:Q15はオフです。

したがって、閾値は

Vth = VCC × ( R2 + R3 ) / ( R1 + R2 + R3 ) = 2.5V

Vin>Vtとなると、差動対の出力がHiとなりQ15がオンします。

したがって、閾値は

Vtl = VCC × R2 / ( R1 + R2 ) = 1.99V

となります。

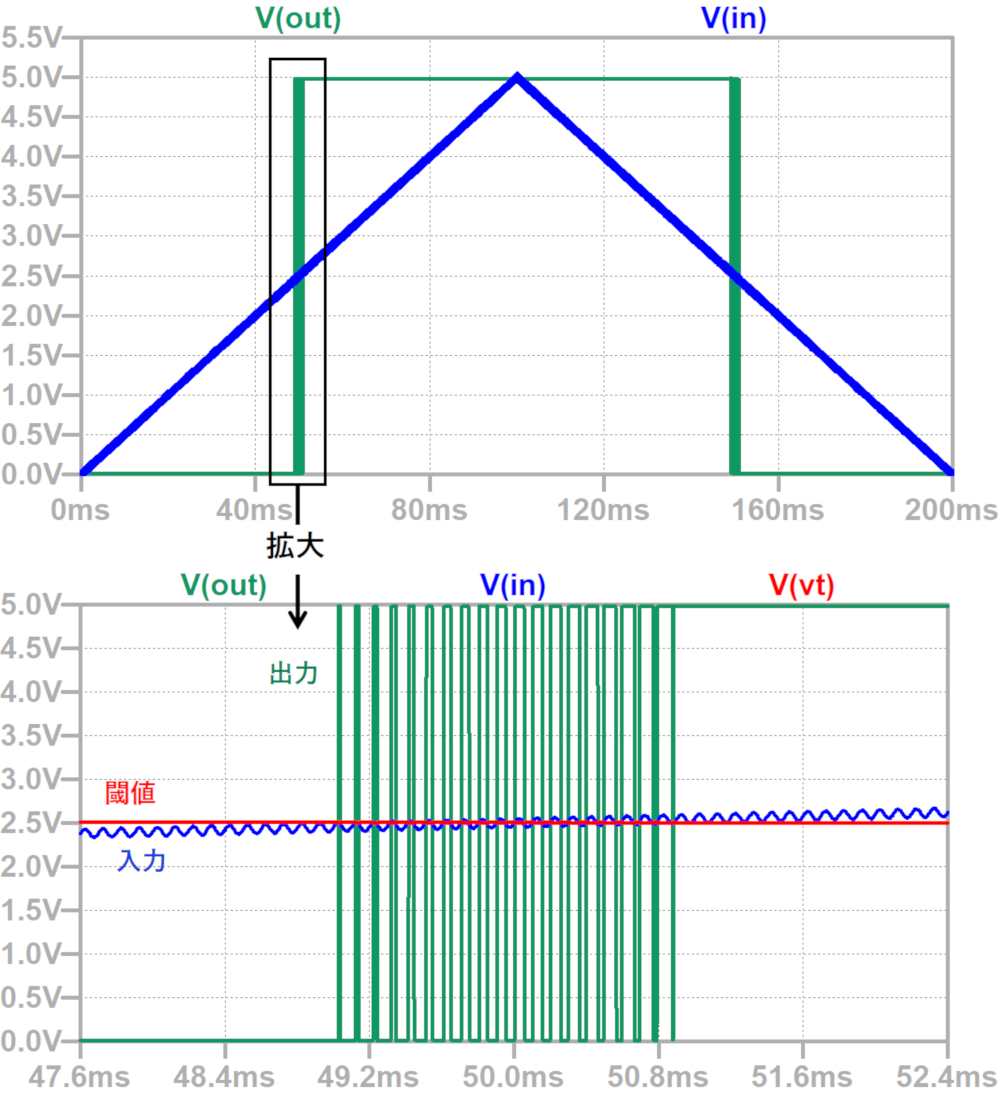

動作確認

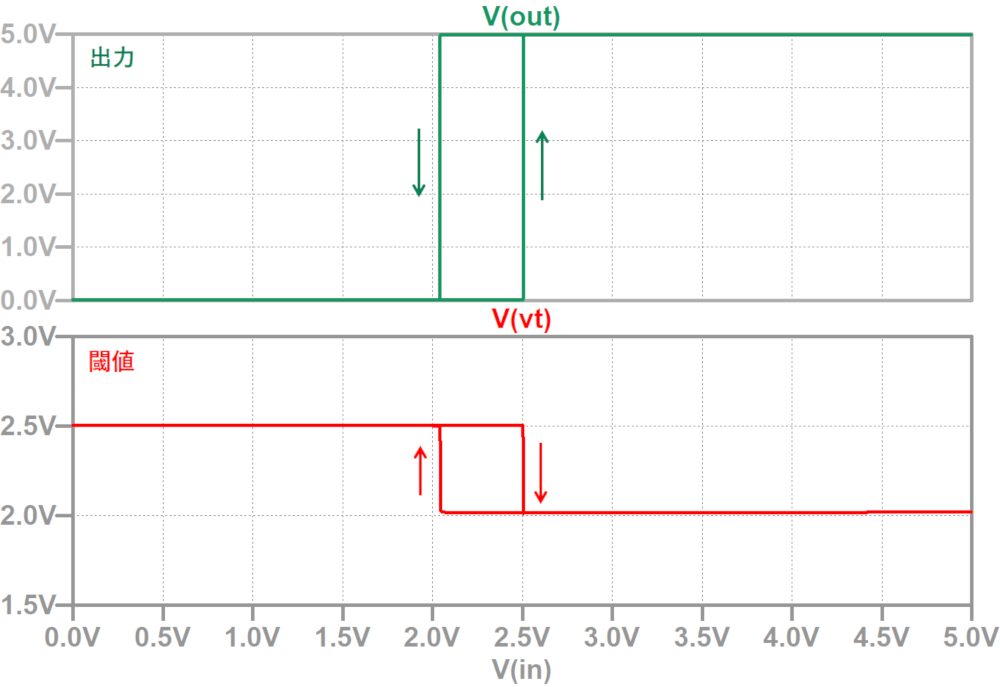

上記回路でシミュレーションを行いました。

横軸をVinとしてDCスイープした波形です。

高い側の閾値は、ほぼ計算通りの値となっています。

低い側の閾値のズレの原因は、

- トランジスタQ15の飽和電圧の影響

- 差動対のバランスのズレ

- 入力側のベース抵抗の影響

などがあり、実際の回路ではさらに、ペアトランジスタの特性差や分圧抵抗比のズレ、電源電圧のばらつきなども閾値のズレに影響を与えます。

オペアンプとの違い

オペアンプとコンパレータは、回路記号が同じで内部回路も似た構成になっています。

大きな違いは2つあります。

- 位相補償回路があるので応答が遅い

- ヒステリシスが無い

オペアンプをコンパレータの代用として使えるか?

基本的には代用として使わない方が良いでしょう。

オペアンプにはヒステリシスが無いので、チャタリングが起こる可能性があります。

入力波形が十分デジタル化された波形であれば、オペアンプで代用しても問題ない場合もありますが、コンパレータICを使った方が安全に設計できます。