DCDCコンバータICの内部回路動作をシミュレーション波形を使って解説

DCDCコンバータIC(スイッチングレギュレータ)の内部回路は、次のようなブロックで構成されています。

- エラーアンプ

- スロープ生成回路

- PWMコンパレータ

- クロック生成回路

- PWM制御ロジック

- ゲートドライバ

- スイッチングFET

これらの内部ブロックの動作をシミュレーション波形を使って解説していきます。

内部回路の動作原理を理解することで、DCDCコンバータに対する理解を深めることができるでしょう。

シミュレーション用の等価回路はLTspiceを使って作成しています。

以下からダウンロードして実際に動作させて確認してみてください。

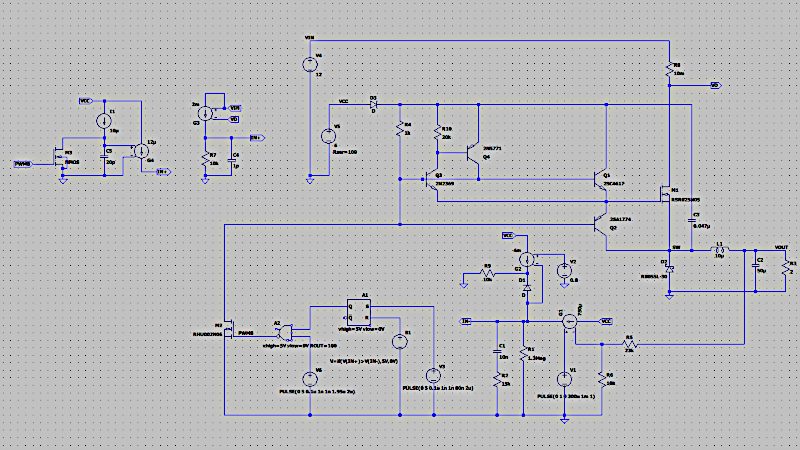

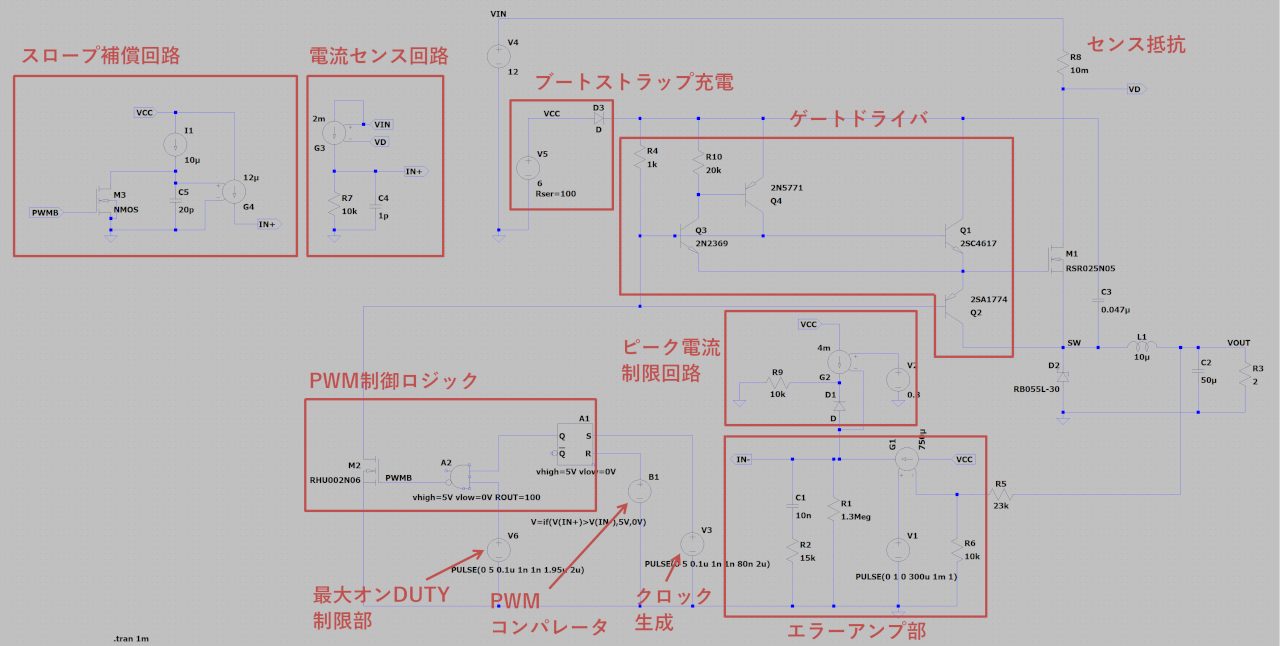

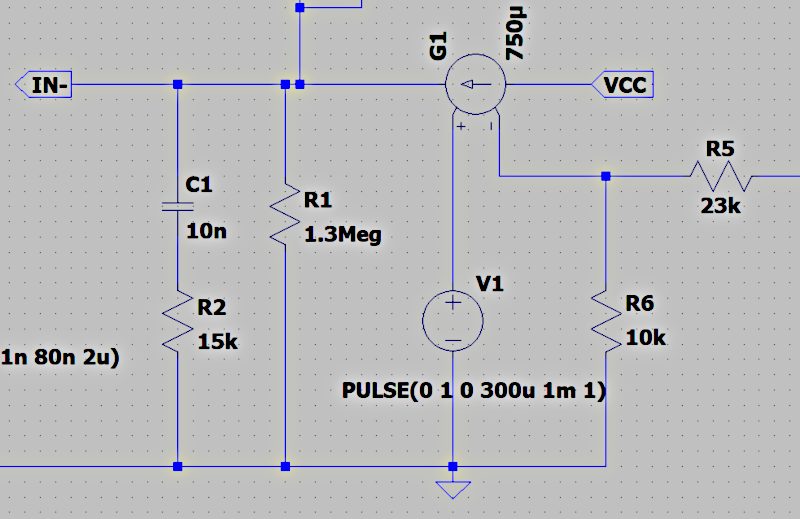

全体回路図

今回作成した回路図は下図のようになります。

降圧型非同期整流スイッチングレギュレータで、制御方式は電流モードです。

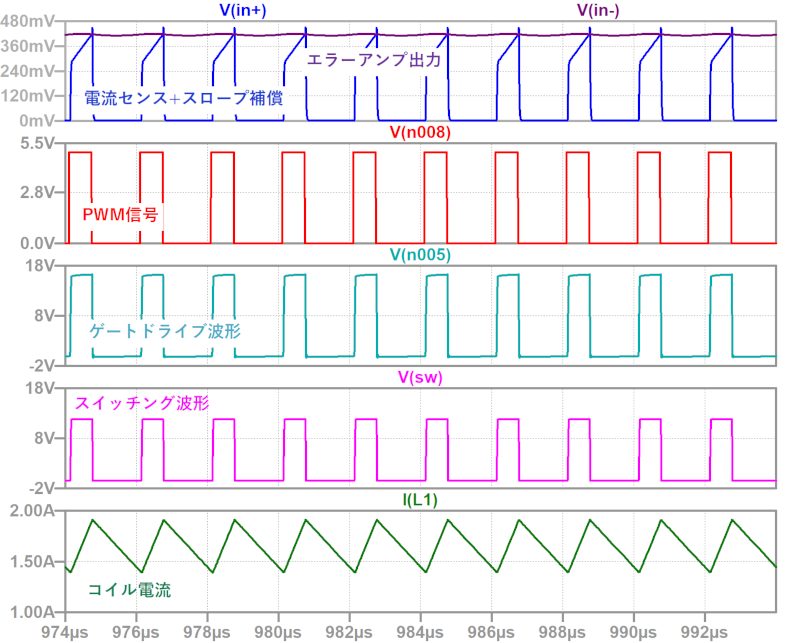

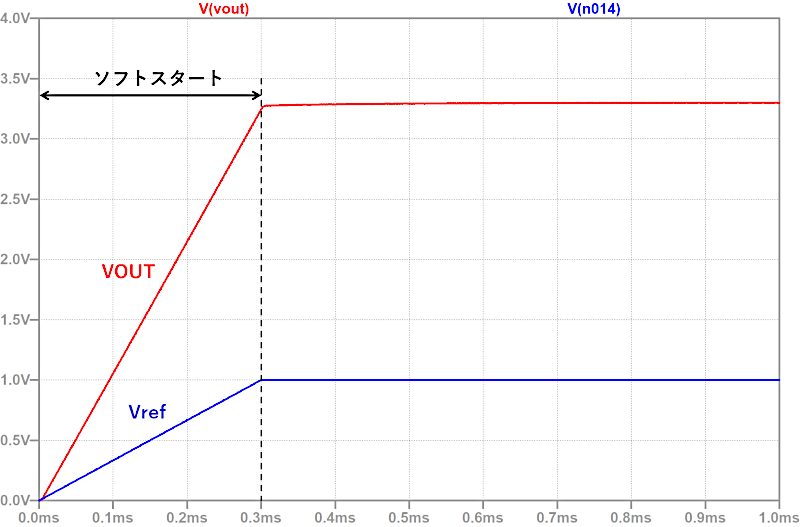

全体の動作波形は下図のようになります。

それでは、各ブロックごとに細かく動作を見ていきましょう。

エラーアンプ部

エラーアンプのGmは750uA/V、出力インピーダンスは1.3MΩで設定しています。

ソフトスタート回路は基準電圧源をゆっくり立ち上げることで代用しています。

スロープ生成部

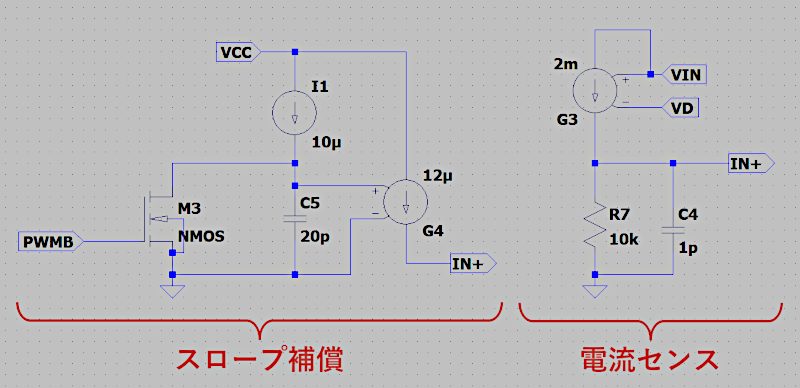

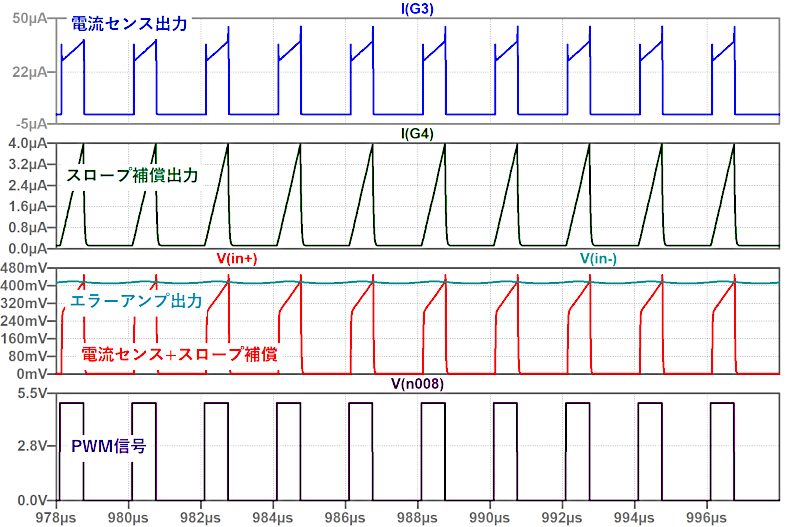

ハイサイドFETの電流をセンスしたものと、スロープ補償用電流生成部です。

スロープ補償とは?DCDCコンバータのサブハーモニック発振を対策

スロープ補償は、コンデンサを定電流で充電して傾きを決め、その電圧をV/I変換して出力、電流センス出力と足し合わせています。

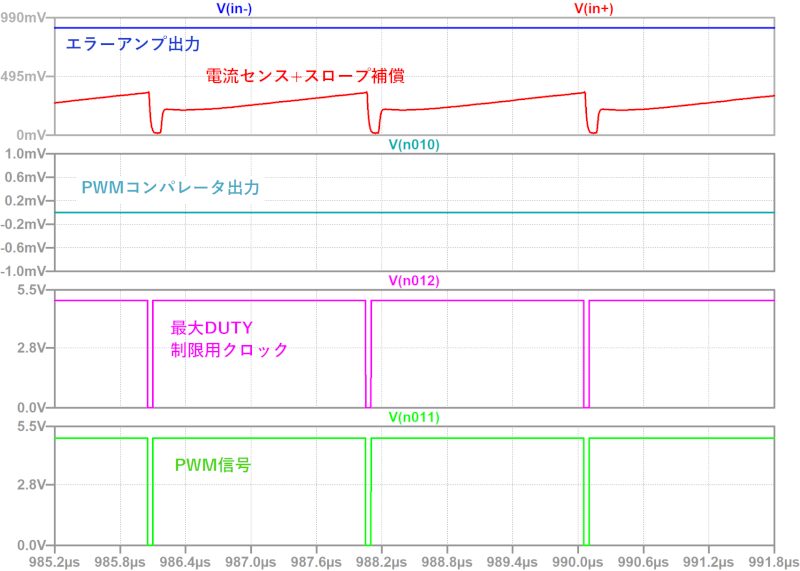

合成された信号とエラーアンプ出力電圧を比較することで、PWM波形が生成されます。

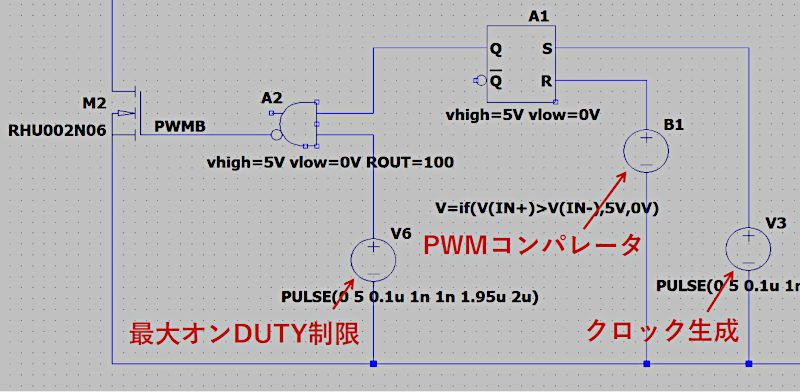

PWM制御ロジック

PWMコンパレータはビヘイビア電源を使って作っており、スロープ電圧がエラーアンプ出力を超えるとHiを出力します。

クロックは、スイッチング周期で短いHiパルスを出力し、フリップフロップのセット端子へ入力します。

今回、出力FETはNch MOSを使用していますので、100%オンを許可するとブートストラップが放電されてしまってオンできなくなります。

そのため、最大オンDUTYに制限をかける回路を追加しています。

DUTYが97.5%に達すると、エラーアンプ出力よりスロープ出力電圧が低くても強制的にPWM信号をLoにしています。

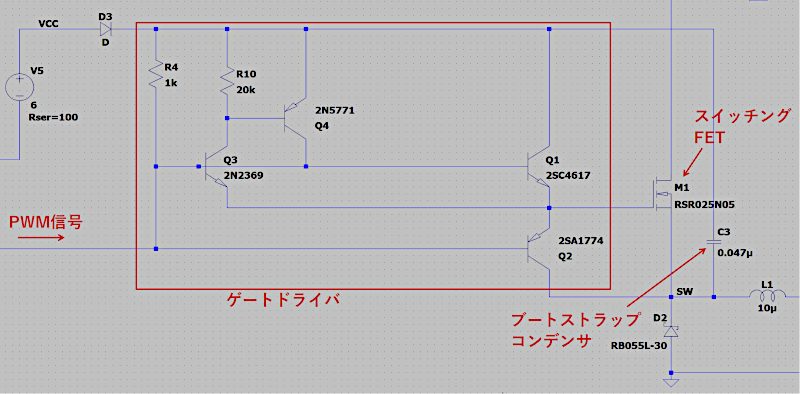

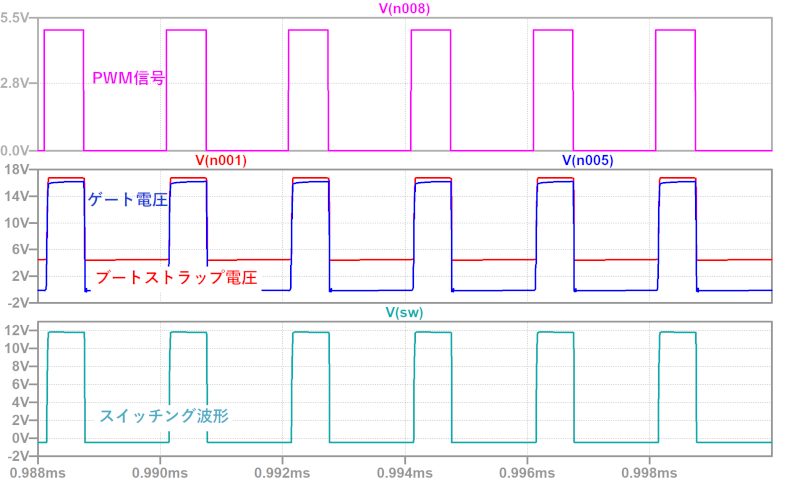

ドライバ部

出力のNch MOSFETを駆動するためのドライバ回路です。

Nch MOSFETをフルオンさせるためにブートストラップでドライバの電源を作っています。

電流制限回路

電流モードの場合、エラーアンプの出力をクランプするだけで電流制限をかけることができます。

今回の回路では、953mVでクランプされるようになっています。

エラーアンプ出力からSW端子までの電流増幅率は5A/Vに設定していますので、ピーク電流は、

0.953V × 5A/V = 4.765A

で制限がかかる計算になります。

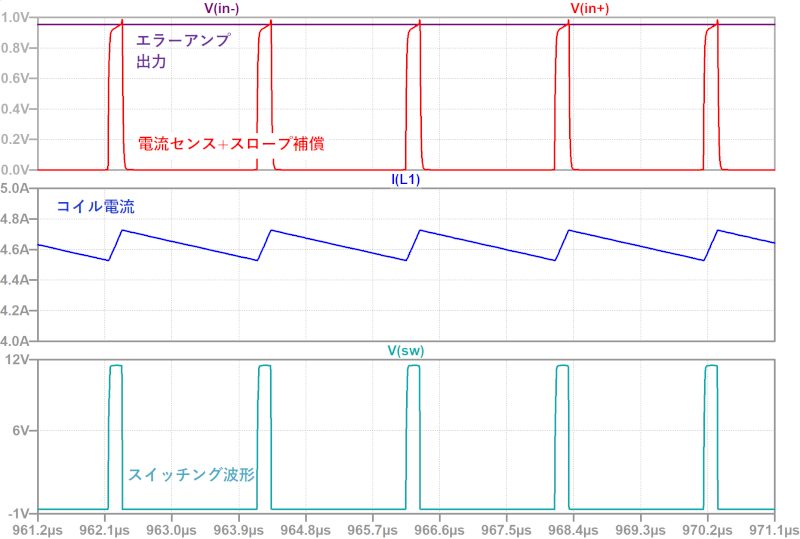

下図は、出力を0.1Ωでショートした場合の電流制限波形です。