シリーズレギュレータの内部回路と動作原理を解説

シリーズレギュレータ(LDO)の基本的な内部回路の紹介と動作原理について解説していきます。

ブロック図と内部回路

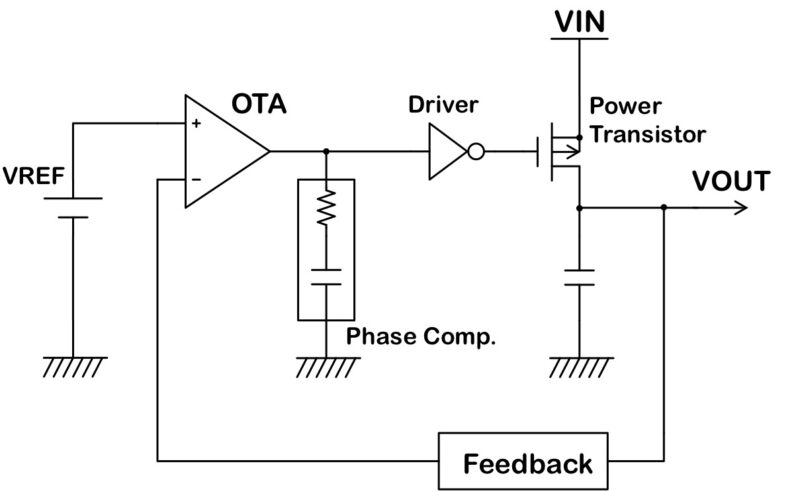

シリーズレギュレータの等価回路は下図のようなブロック図で表すことができます。

大まかな構成部品は、

- 基準電圧源

- 差動増幅器

- 位相補償回路

- 増幅段

- パワートランジスタ

- フィードバック部

となります。

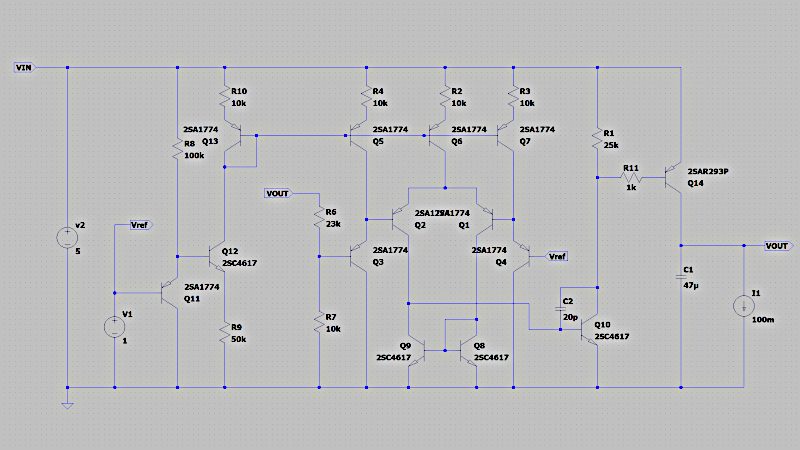

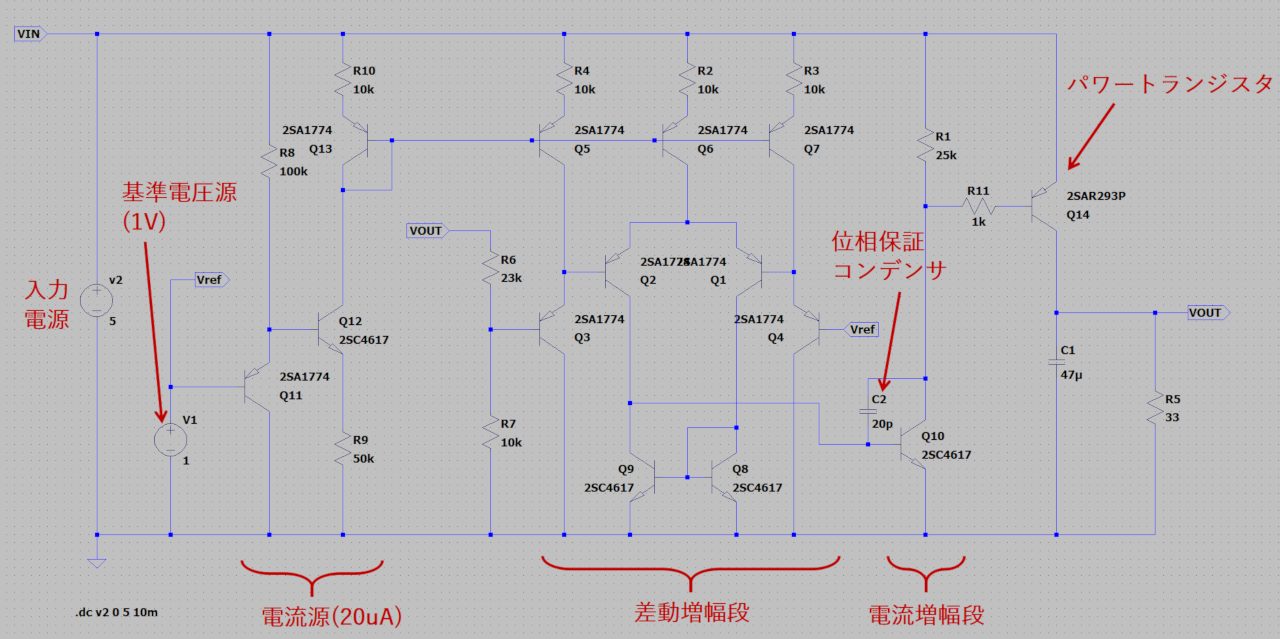

これをトランジスタレベルで描くと下図のような内部回路になります。

※実際にシミュレーションで動作を確認したい方は、下記より回路図をダウンロードしてLTspiceで読み込んでください。

動作原理

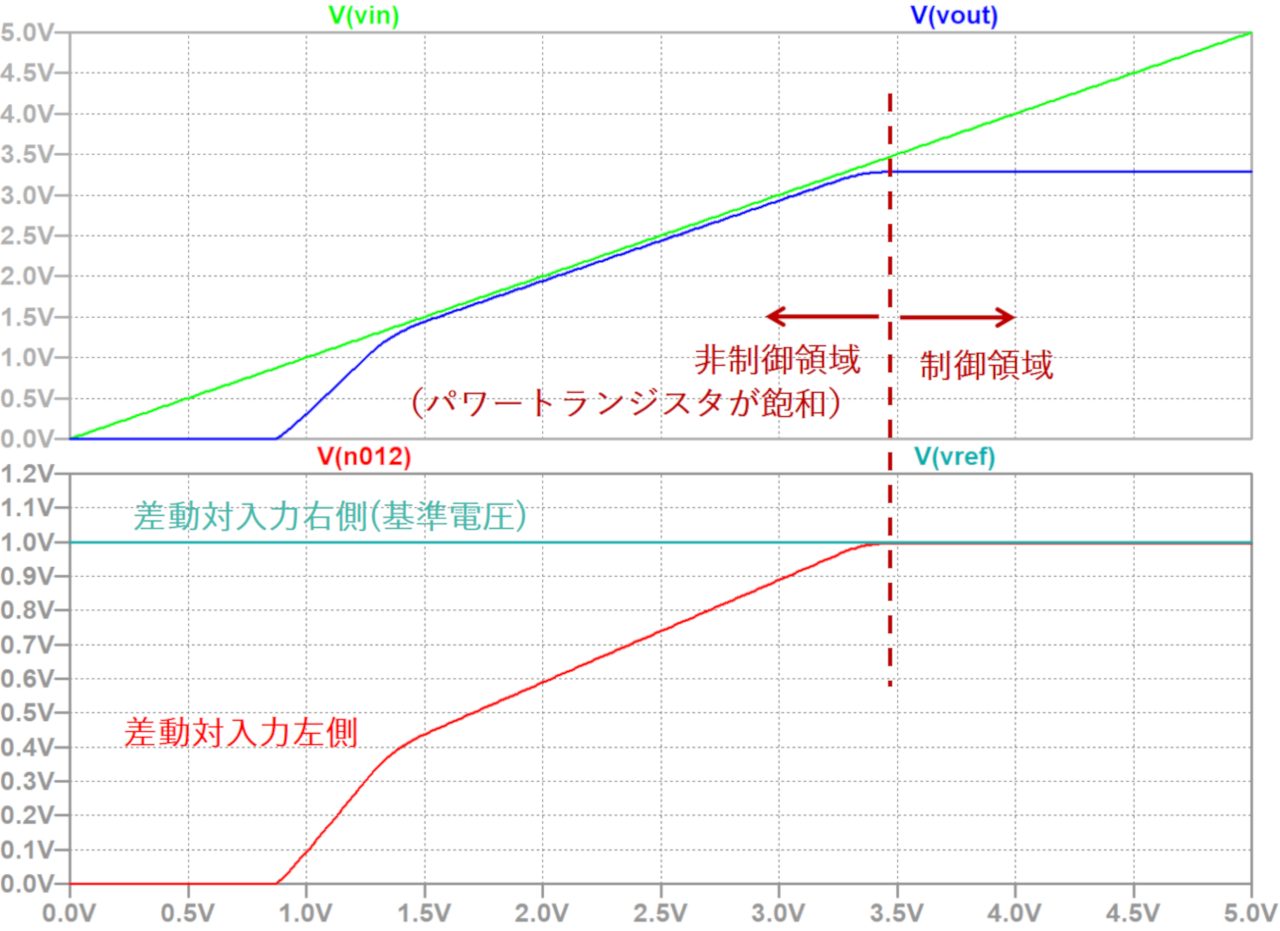

前記の回路図で入力電源を0V⇒5Vにスイープさせて動作を確認します。

出力電圧は3.3V設定のため、入力電圧が3.3Vよりも低い領域では差動増幅器の入力電圧は基準電圧側(右側)が高い状態となります。

電流は差動対の左側に全て流れ、電流増幅段のトランジスタQ10のベースへ流れ込みます。

これによりQ10はフルオンして電流を引き込み、パワートランジスタが飽和し、VIN≒VOUTの状態が継続します。

VINが3.3Vより高くなるとVOUT=3.3Vで固定され、制御領域に入ります。

この状態では、オペアンプのバーチャルショートの考え方と同様で、差動対の両方の入力電圧が等しい状態です。

ですが、実際には差動対の左側の電圧がやや低くなります。

出力に必要な電流をドライブするため、差動対を左側へ傾け、電流増幅回路を経由してパワートランジスタのベース電流を供給するためです。

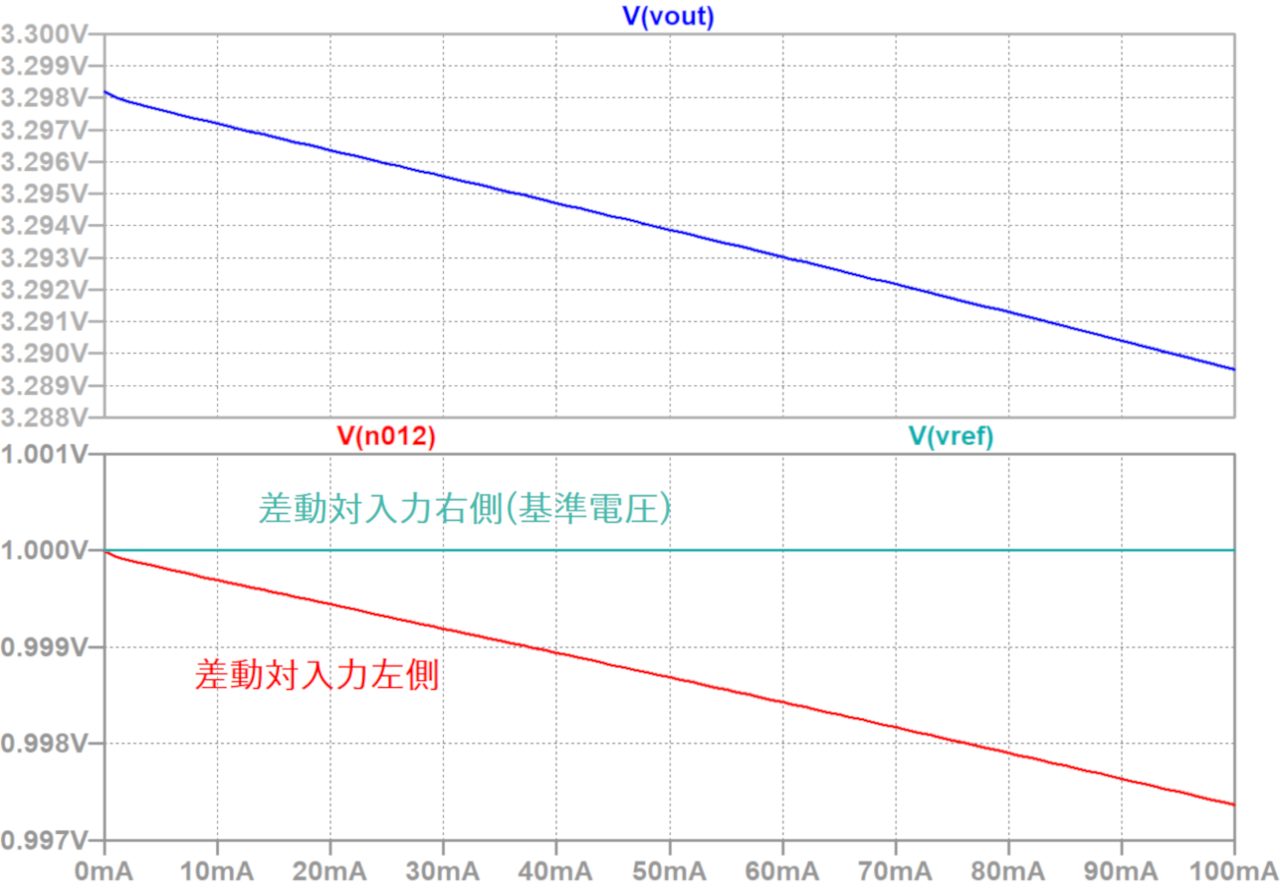

出力電流をスイープさせたシミュレーション波形が下図になります。

出力電流が大きいほど差動対の左側の電圧を低くする必要があるので、出力電流が大きいほど出力電圧が低下することになります。

これがロードレギュレーションが発生するメカニズムです。

回路の増幅率が高いほど差動対の差電圧は小さくて済むため、ロードレギュレーションは小さくなります。

バーチャルショートは増幅率が無限大という理想条件で考えているため、差動入力の差がゼロと考えることができるのです。