過電圧保護とは?回路構成と機能を解説

過電圧保護とは、外部からのサージ電圧から内部回路を守るための回路、またはデバイスの異常で出力が過電圧状態になった際に後段デバイスを保護するための機能です。

OVP(Over Voltage Protection)と呼ばれたり、OVLO(Over Voltage Lock Out)と記載される場合もあります。

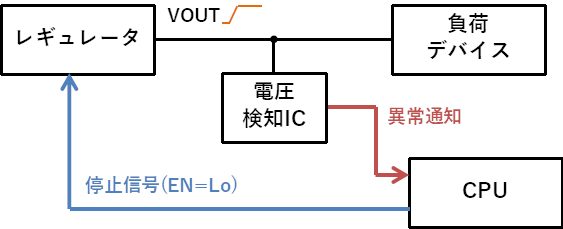

電圧検知ICを使った過電圧保護

主にレギュレータの出力異常による過電圧から後段デバイスを保護するため、電圧検知IC(リセットIC)でレギュレータの出力電圧を監視し、異常をCPUへ通知してCPUからレギュレータを停止させる方式です。

検知ICから直接レギュレータを停止させない理由は、停止⇒電圧低下⇒停止解除⇒過電圧…を繰り返してしまうためです。

そのため、CPUを介してレギュレータの停止を維持し、電源再投入時にリスタートさせるなどの処理を行います。

各メーカーの電圧ICにどのようなものがあるかは、こちらをご覧ください。

電圧検知IC(リセットIC)一覧

レギュレータICに内蔵される過電圧保護

LDOやDCDCコンバータ(スイッチングレギュレータ)に内蔵される過電圧保護のタイプは、

- 異常通知タイプ

- 電圧クランプタイプ

- ラッチオフタイプ

などがあります。

異常通知タイプ

最もベーシックなタイプで、設定されたしきい値以上の電圧を検知すると異常と判断し、CPUへ異常通知信号を発行します。

マイコンからはEnable=Loを出力し、レギュレータを停止させます。

電圧クランプタイプ

一定以上に出力電圧が持ち上がらないようにクランプするタイプです。

後段の負荷デバイスの絶対最大定格以下にクランプ電圧を設定することで破壊を防ぎます。

同時に異常通知を行うICもあります。

ラッチオフタイプ

過電圧を検知するとラッチオフするタイプです。

CPUによる制御が行えない場合に有効です。

入力電源やEnable信号のトグルにより復帰します。

ディスクリート部品で組む過電圧保護回路

ICの外部でトランジスタやツェナーダイオードなどを使って自作する簡易的な過電圧保護回路を紹介します。

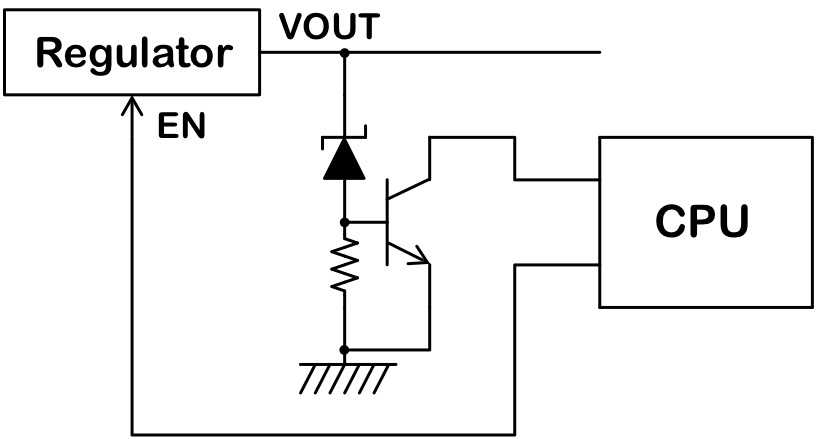

過電圧検知のみ

レギュレータの出力電圧がツェナー電圧+トランジスタのVBEを超えると両素子がオンします。

NPNトランジスタのコレクタ側をCPUへの異常通知信号として使い、CPUからレギュレータをオフさせます。

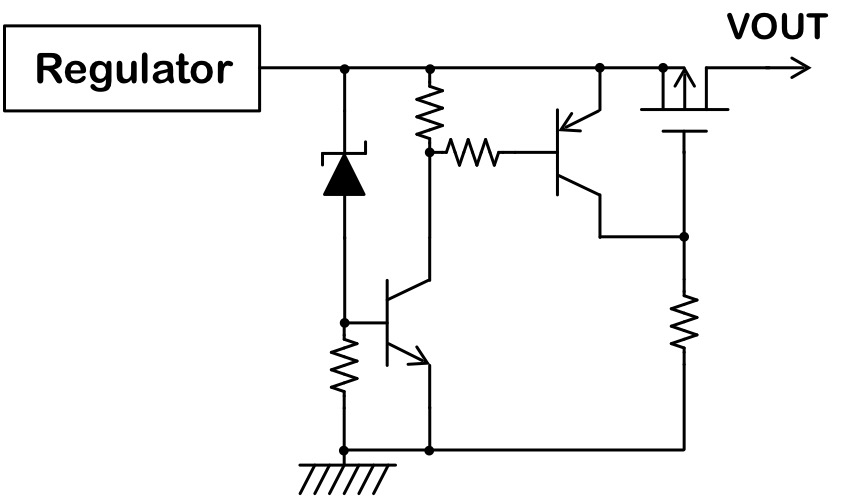

FETを使って負荷と切り離す

検知方式は先程と同じでツェナー電圧とトランジスタのVBEで決まります。

過電圧を検知するとレギュレータ出力と負荷デバイスの間にあるMOSスイッチをオフさせることで負荷デバイスを過電圧から保護します。

CPUを介さないためレギュレータは動作し続けますので、レギュレータ端の過電圧状態は継続します。

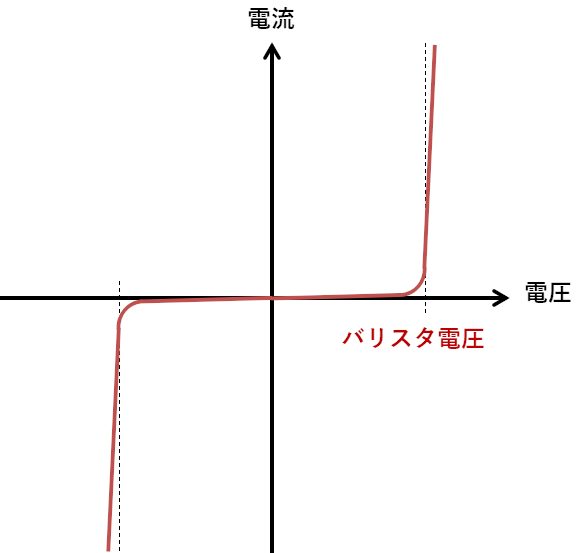

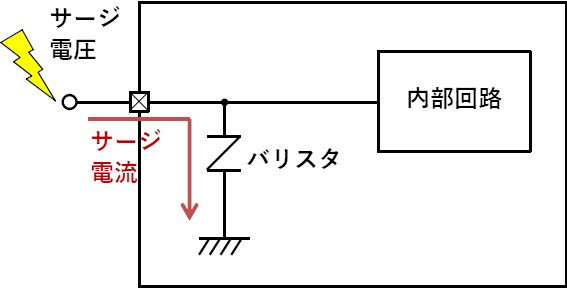

バリスタを使ったサージ保護回路

バリスタとは、印加される電圧が一定を超えると電流が一気に流れ、電圧をクランプする素子です。

落雷や静電気(ESD)、車のロードダンプなどによる高電圧(サージ電圧)から機器を保護する目的として使われます。

バリスタは、下図のような電圧電流特性を持ちます。

過渡的な高電圧が印加される可能性がある端子の入り口付近に設置し、内部回路を保護します。

サージ電流はバリスタ側へ流れ、電圧はバリスタ電圧によりクランプされるため内部回路が保護されます。