SEPICの動作原理と設計方法

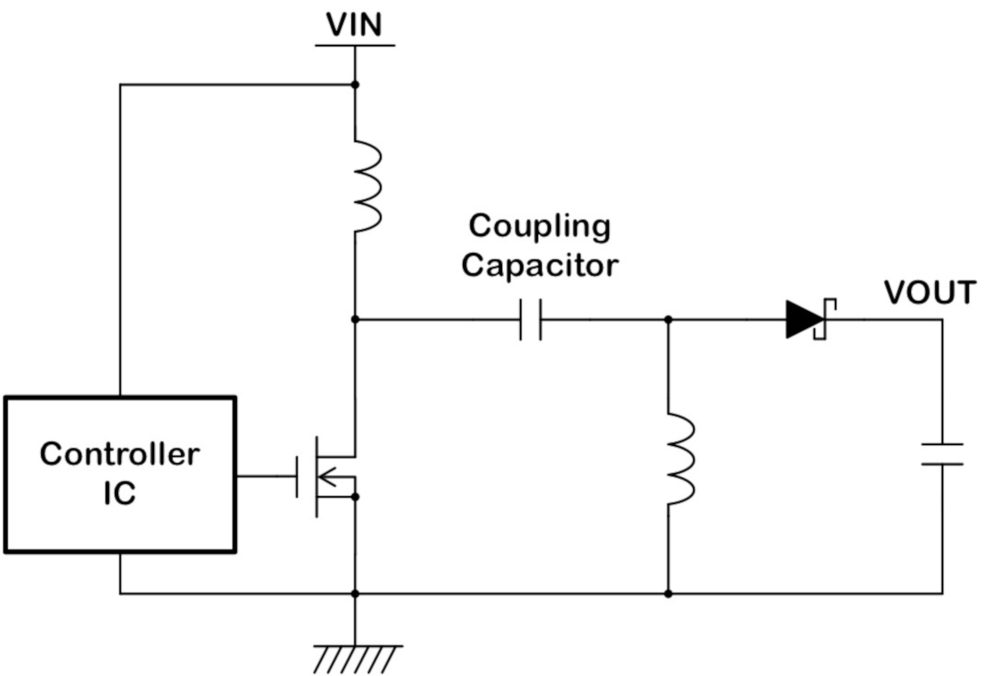

SEPICとは、Single Ended Primary Inductor Converterの略で、スイッチングMOSFET1つとコイル2つで構成される昇降圧可能なスイッチングレギュレータの方式の1つです。

MOSFETを4つ使うHブリッジ型の昇降圧コンバータと比べ制御が簡単であるというメリットがあります。

本稿ではSEPICの動作メカニズムと設計の手順について解説していきます。

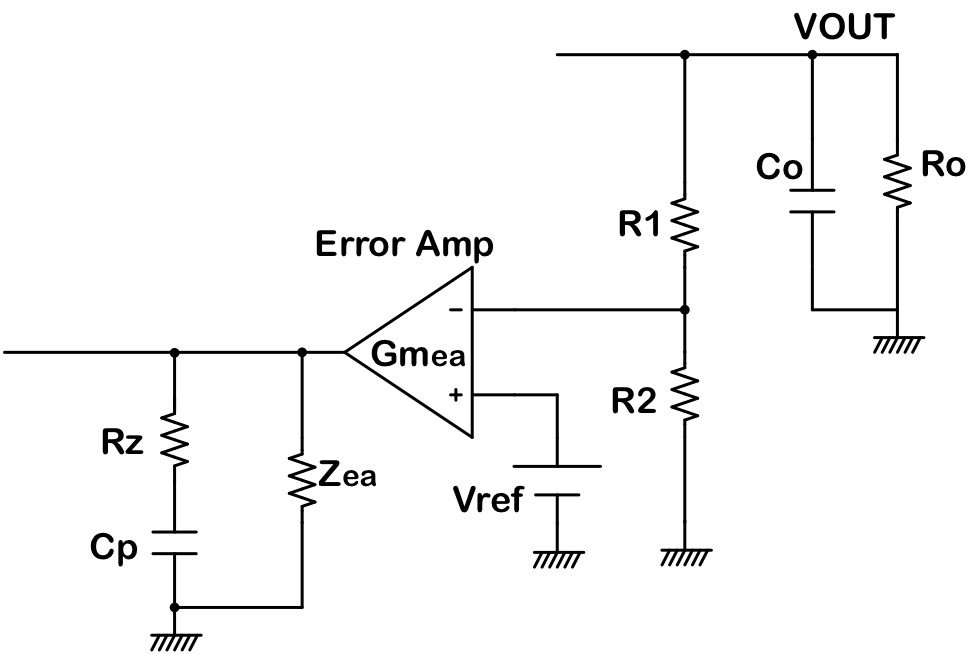

SEPICの回路構成

SEPICは、コイルを2つ使い構成されます。

カップリングコンデンサは入力と出力をDC的に分離します。

フライバックの1次側と2次側をカップリングコンデンサで接続したような構成になっています。

コントローラICは、SEPIC専用のものはなく、昇圧DCDCコンバータ(またはコントローラ)を使います。

ただし、SEPICとして使えないICもあるので、採用の際には確認しておく必要があります。

SEPICの動作原理

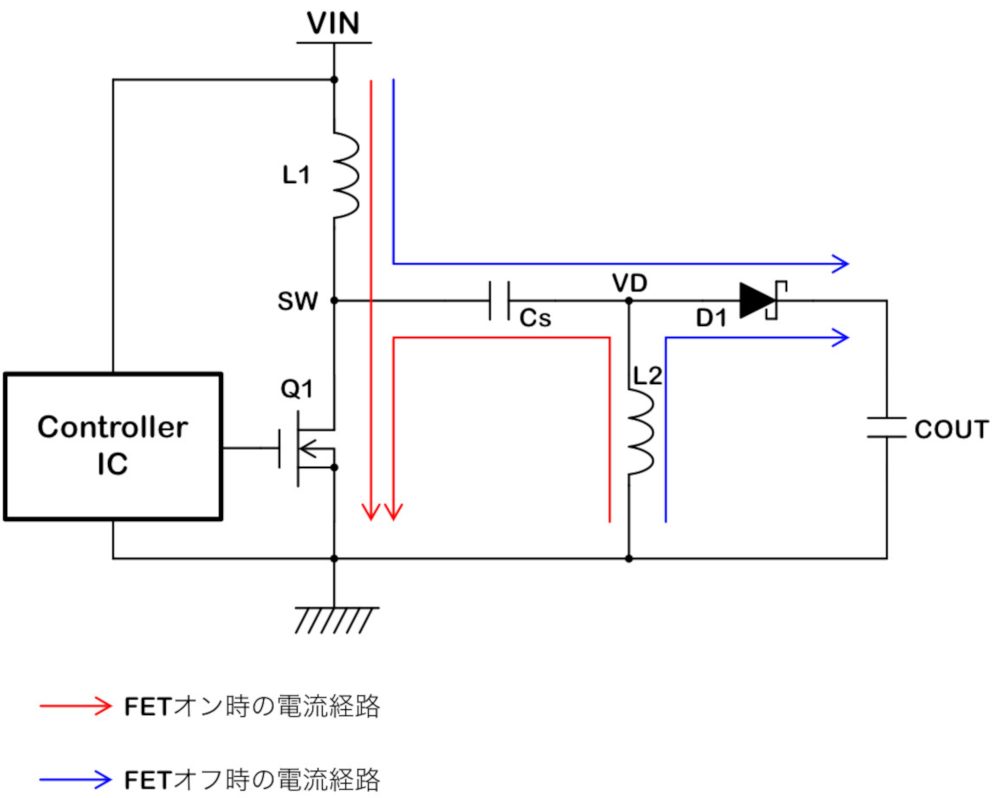

MOSFETのオン・オフ時の電流経路を示します。

MOSFETオン時には2つのコイルから電流を引き込み、コイルにエネルギーが溜まります。

オフ時にはコイルに溜まったエネルギーが出力側へ転送されます。

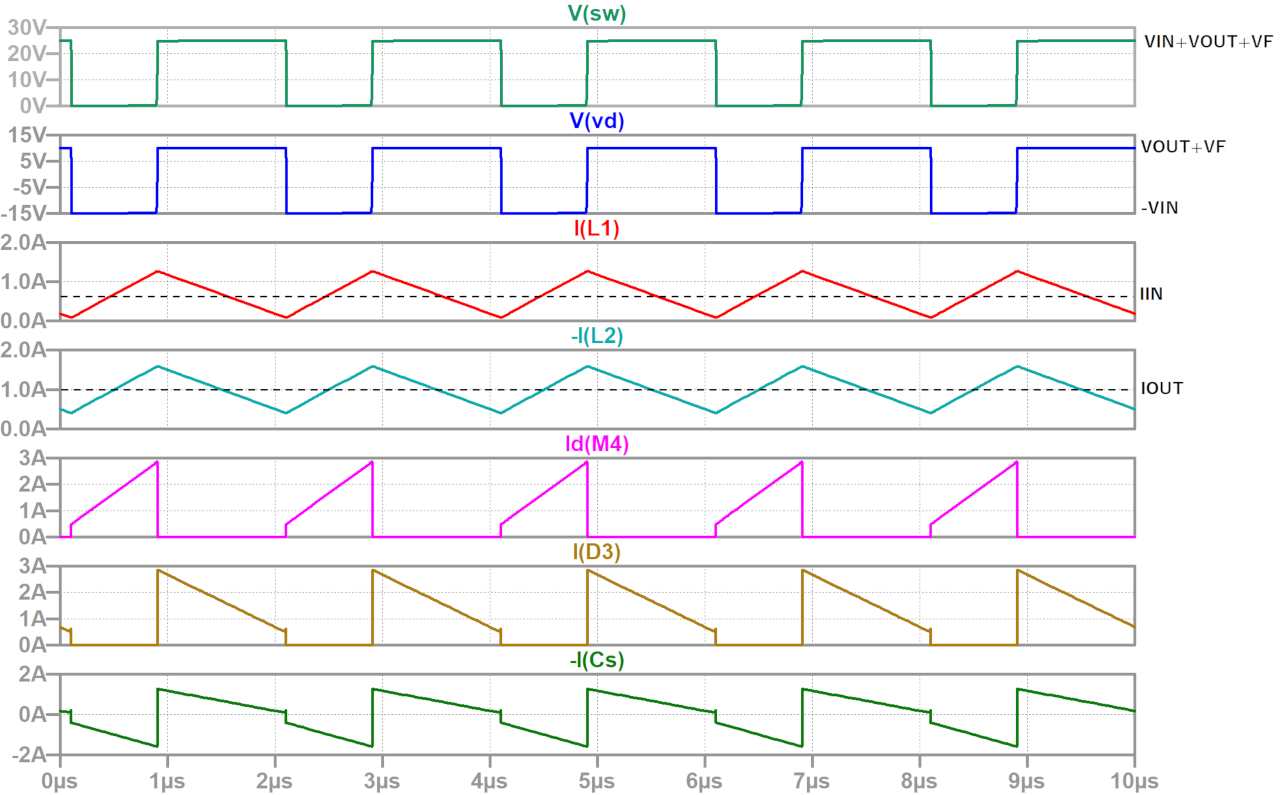

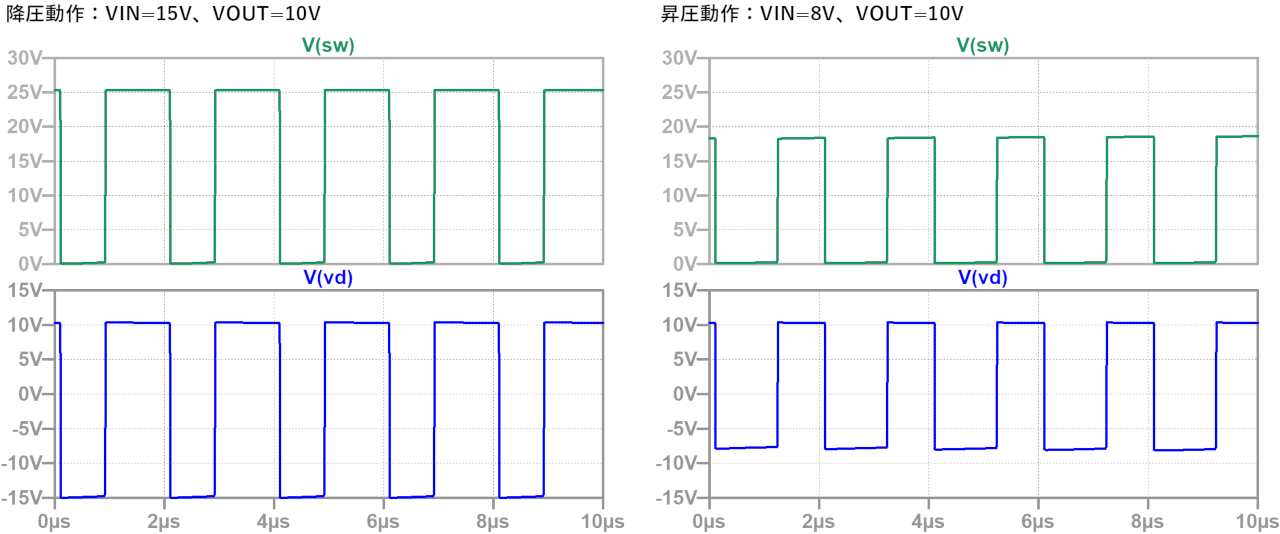

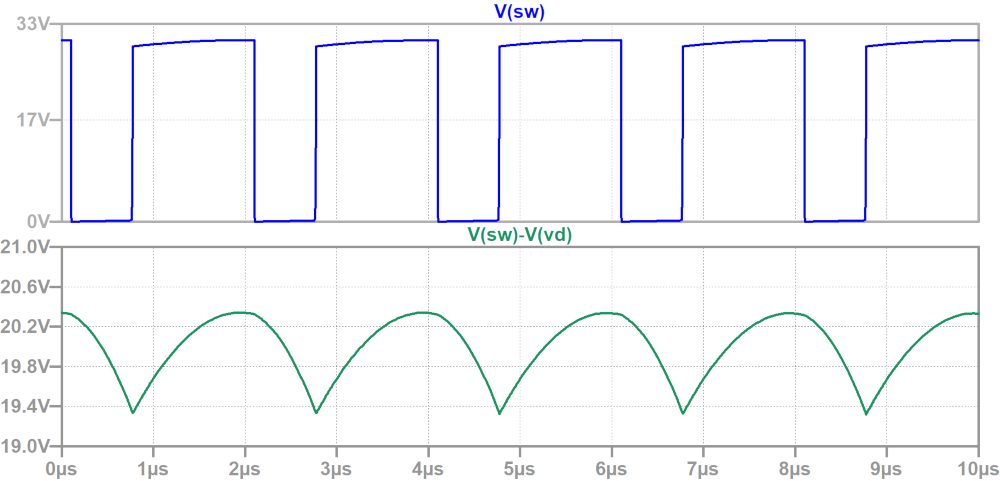

各点の電圧波形と電流波形を示します。

(条件:VIN=15V、VOUT=10V、IOUT=1A、Fsw=500kHz)

MOSFETがオンすると、SW電圧は0Vに引き下げられ、L1にはVINの電圧がかかります。

カップリングコンデンサ:Csにより、VDの電圧が-VINまで引き下げられるため、L2にもVINの電圧がかかることになります。

MOSFETオフ時には、出力側へ電流が流れるため、VDの電圧はショットキーダイオードでクランプされ、VOUT + VF となります。

SW電圧はVIN + VOUT + VFまで上昇します。

オフ時にL1、L2にかかる電圧はどちらも-(VOUT + VF)となります。

したがって、インダクタンスが等しければ、L1、L2のリップル電流が等しくなります。

L1に流れる電流の平均値が入力電流となり、L2に流れる平均電流が出力電流と等しくなります。

SEPICが昇降圧可能な理由はカップリングコンデンサにあります。

波形をご覧頂ければ分かる通り、SW端子とVD端子の電圧振幅は等しくなっています。

つまり、カップリングコンデンサによってDC電圧のレベルシフトが行われているということです。

VD電圧のHiレベルは出力電圧でクランプされ決まるため、VINによってLoレベルが決まります。

入力電圧を変え、降圧動作と昇圧動作の波形を比較したものを下図に示します。

SEPICの設計手順

SEPICの設計計算、部品選定の手順について解説していきます。

条件は、VIN=8V~20V、VOUT=10V、IOUT=1A、Fsw=500kHzとします。

LTspiceのシミュレーション回路は下記よりダウンロードして頂けます。

1.DUTYの計算

はじめに、設定した条件でのDUTYサイクルを計算します。

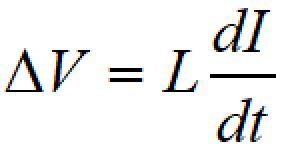

コイルの基本式は、

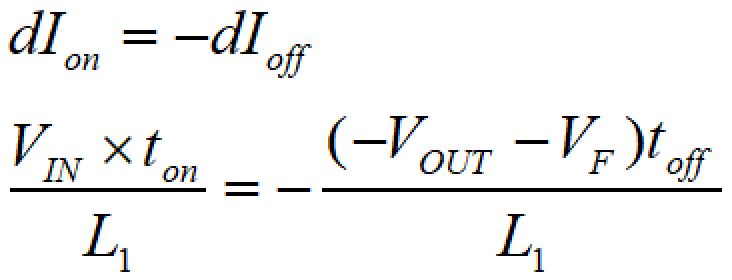

オンサイクルとオフサイクルのコイル電流の変動量が等しいことから

tonがFETのオン時間、toffがオフ時間です。

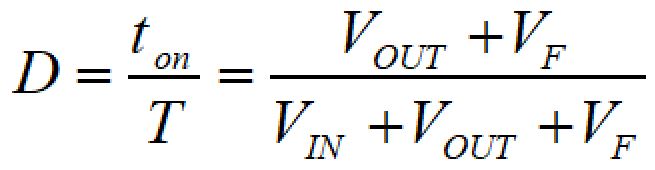

スイッチング周期をTとすると、

これを代入して整理すると、

となります。

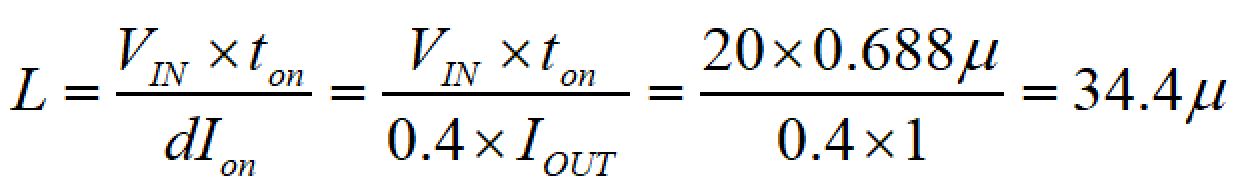

2.インダクタの選定

明確な基準があるわけではありませんが、インダクタのリップル電流が最大出力電流の40%程度になるようなインダクタンスを選びます。

コイルの基本式より、

よって、インダクタンスは33uHを選択します。

3.MOSFETの選定

先述の通り、SW端子電圧(MOSFETのドレイン電圧)はVIN + VOUT + VFまで上昇するため、それ以上の耐圧を持った製品を選定する必要があります。

ドレインにかかる最大電圧は、20V+10V+0.5V=30.5Vです。

MOSFETに流れる電流はIIN + IOUTになります。

効率:η=80%とすると、IINは、

したがって、MOSFETに流れる最大電流は2.56Aとなります。

電圧、電流と損失を考慮に入れてMOSFETを選定します。

4.ダイオードの選定

MOSFETオン時にはVDの電圧が-VINまで低下するため、ショットキーダイオードの逆耐圧はVIN + VOUT以上が必要になります。

ダイオードに発生する損失は、VF=0.5Vとすると、

Pd = VF × IOUT =0.5W

となります。

カップリングコンデンサがあるため、出力がデッドショートしてもダイオードに電流が流れ続けることはありませんが、ハーフショートまで考慮するなら、電流制限値のMAXまでの電流定格を持たせる必要があります。

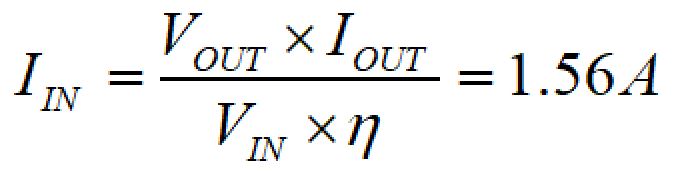

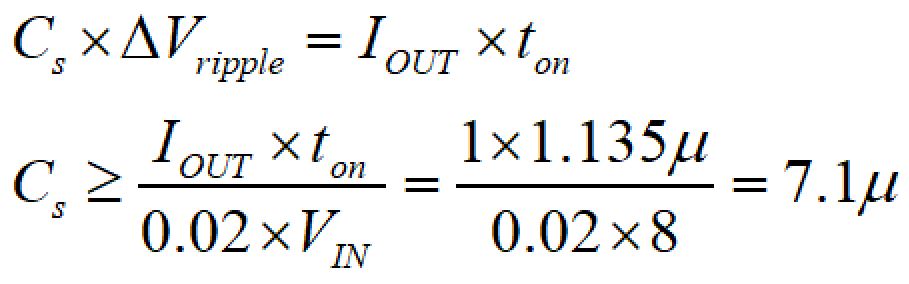

5.カップリングコンデンサの選定

カップリングコンデンサの充放電により、リップル電圧が発生します。

リップル電圧が大きいと発振しやすくなるため、できるだけ小さくする必要があります。

明確な基準はありませんが、リップル電圧はVIN_minの2%以下になるように設定します。

容量は、コンデンサの基本式から以下のように計算できます。

よって、カップリングコンデンサは8.2uFを選定します。

ただし、DCバイアス特性を考慮してこれ以上の容量を確保できている必要があります。

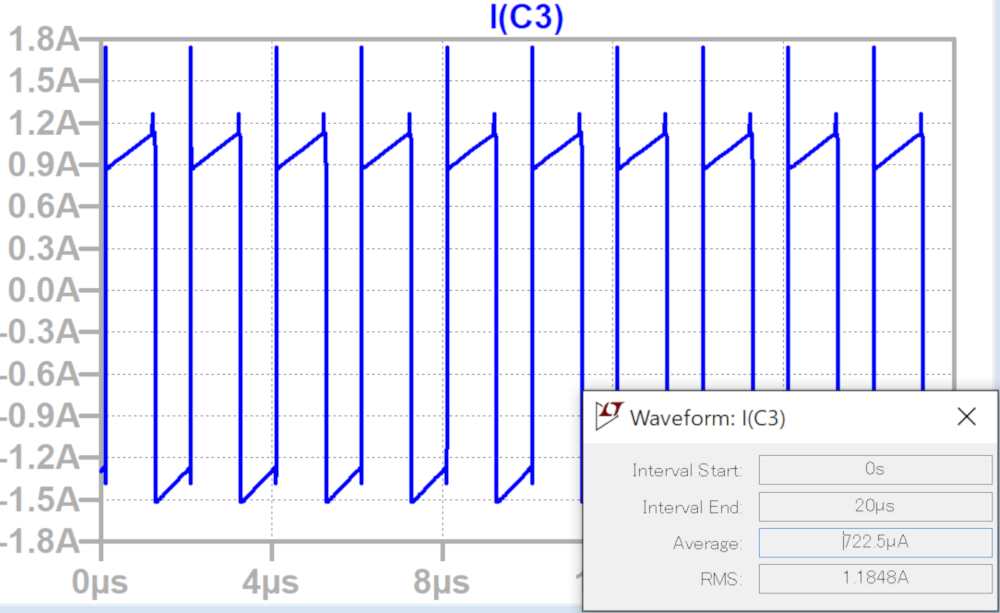

次に、カップリングコンデンサに流れる電流の実効値を求めます。

台形波となり計算が複雑になりますので、シミュレーションを利用します。

LTspiceでは簡単に実効値を求めることができます。

カップリングコンデンサの電流をモニタし、Ctrlを押しながらラベルをクリックすると、表示領域の平均値や実効値を確認できます。

実効値が1.18Aであることが分かりました。

コンデンサの許容リップル電流が上記値以上のものを選びます。

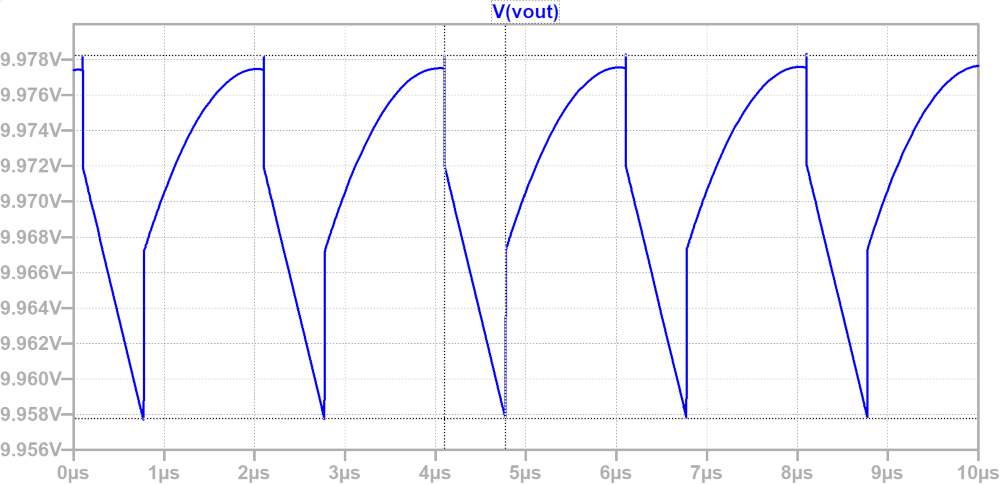

6.出力コンデンサの選定

負荷デバイスの要求リップル電圧以下となるように出力コンデンサ容量を選定します。

昇圧スイッチングレギュレータと同じ考え方でリップルを計算できますが、ここではシミュレーションで確認します。

実効容量が47uF、ESRが5mΩの出力コンデンサの場合、リップル電圧は20.5mVp-pとなりました。

7.位相補償

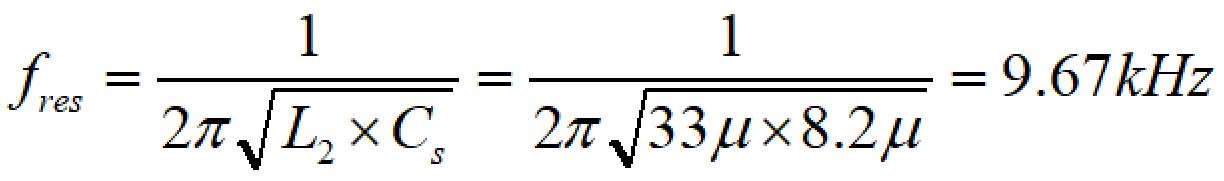

SEPICの位相補償が困難な理由は2つあります。

- L2とCsによる共振ポールが形成される

- L2と負荷によるRHPゼロが形成される

安定化のためには、これらの低い方の周波数の1/10以下にクロスオーバー周波数を設定する必要があります。

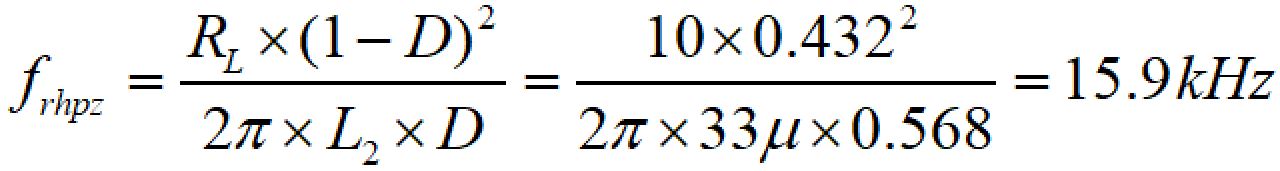

共振ポールの計算

RHPゼロの計算

したがって、クロスオーバー周波数は0.967kHz≒1kHz以下となるようにします。

オープンループゲインから、目標のクロスオーバー周波数となるように1stポール、ゼロの設定を行っていきます。

位相補償はエラーアンプ出力部に接続するCpとRzにより行います。

今回のシミュレーション回路では、各定数は以下のように設定しています。

エラーアンプのトランスコンダクタンス:Gmea=750uA/V

エラーアンプの出力インピーダンス:Zea=1.3MΩ

出力負荷抵抗:Ro=10Ω

フィードバック抵抗:R1=27kΩ、R2=3kΩ

内部基準電圧源:Vref=1V

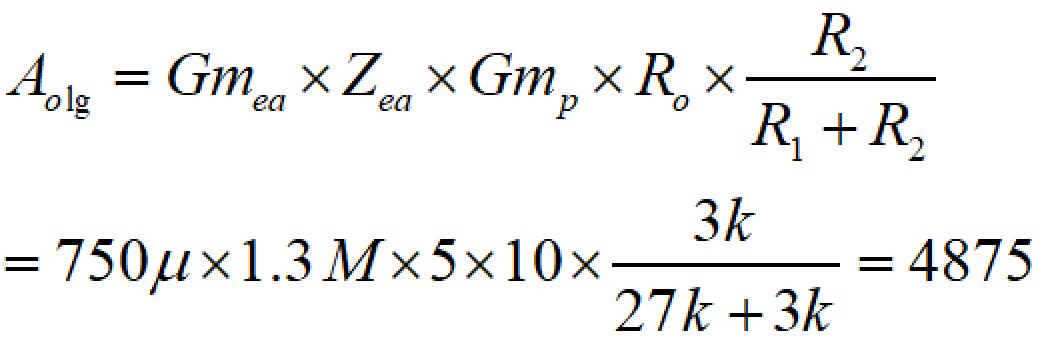

オープンループゲインの計算

1stポールの設定

1stポールの周波数からクロスオーバー周波数まで-20dB/decadeの傾きでゲインが低下していくように設計しますので、1stポールの周波数は、

fp1 = 1kHz / 4875 = 0.205Hz

とする必要があります。

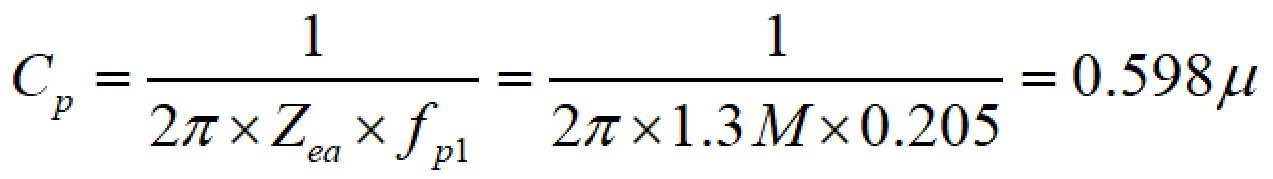

1stポールはCpとZeaで決まりますので、Cpは、

よって、Cp=0.56uFとします。

ゼロの設定

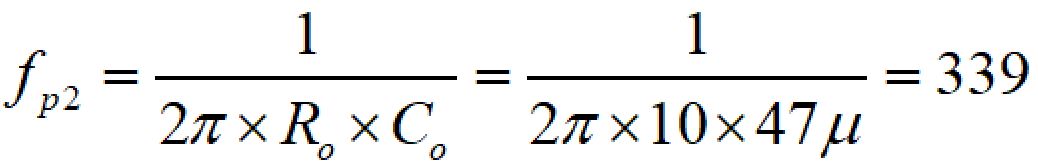

負荷抵抗と出力容量によって2つ目のポールが形成されますが、安定させるためにはこれをゼロで打ち消す必要があります。

2ndポールは、

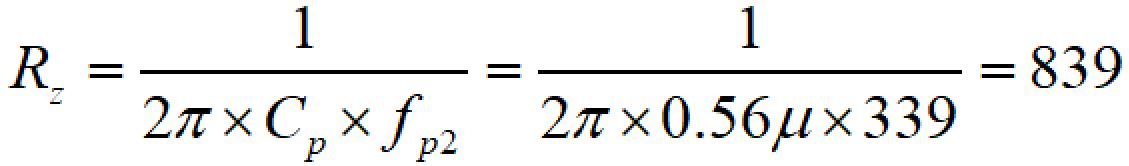

ゼロはCpとRzによって決まり、Rzは、

よって、820Ωとします。

SEPICのメリットとデメリット

Hブリッジ型の昇降圧DCDCコンバータと比べた場合のメリット、デメリットを以下にまとめました。

メリット

- スイッチングFETが1つで済む

- モードの切り替わりが発生せずシームレス

- コントローラICが比較的安価

デメリット

- MOSFETとダイオードにVIN+VOUT以上の耐圧が必要

- コイルが2つ必要

- 位相補償が困難

- 振幅が大きいためノイズも大きくなりやすい

- Hブリッジと比較すると効率が悪い

入力電圧、出力電圧が高いほどMOSFETやダイオードに高い耐圧が求められるため、SEPICの方が高コスト化する可能性があります。

また、効率面で考えても、出力電流が大きいほどSEPICの方が不利になってきます。

用途に応じて使い分けられるように、両方の昇降圧方式について理解しておきましょう。