ファンアウトの意味と計算方法

ファンアウトとは、1つのデジタルIC出力に接続できる入力回路の最大数です。

ファンアウトは出力回路の電流能力で決まり、ファンアウトの小さいICの場合、出力信号が減衰してしまって正常に伝達できなくなります。

本稿ではファンアウトの考え方、計算方法について解説していきます。

ファンアウトの考え方

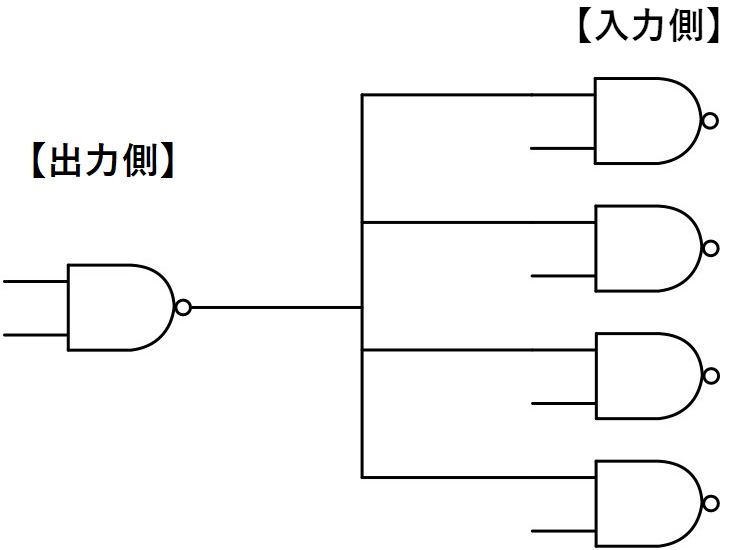

下図のように1つのロジックICの後段に複数のロジックICが接続される場合を考えます。

このとき後段に接続できるICの数(入力回路の数)の最大値がファンアウトです。

ファンアウトはTTLとCMOSで考え方が異なります。

TTLのファンアウト

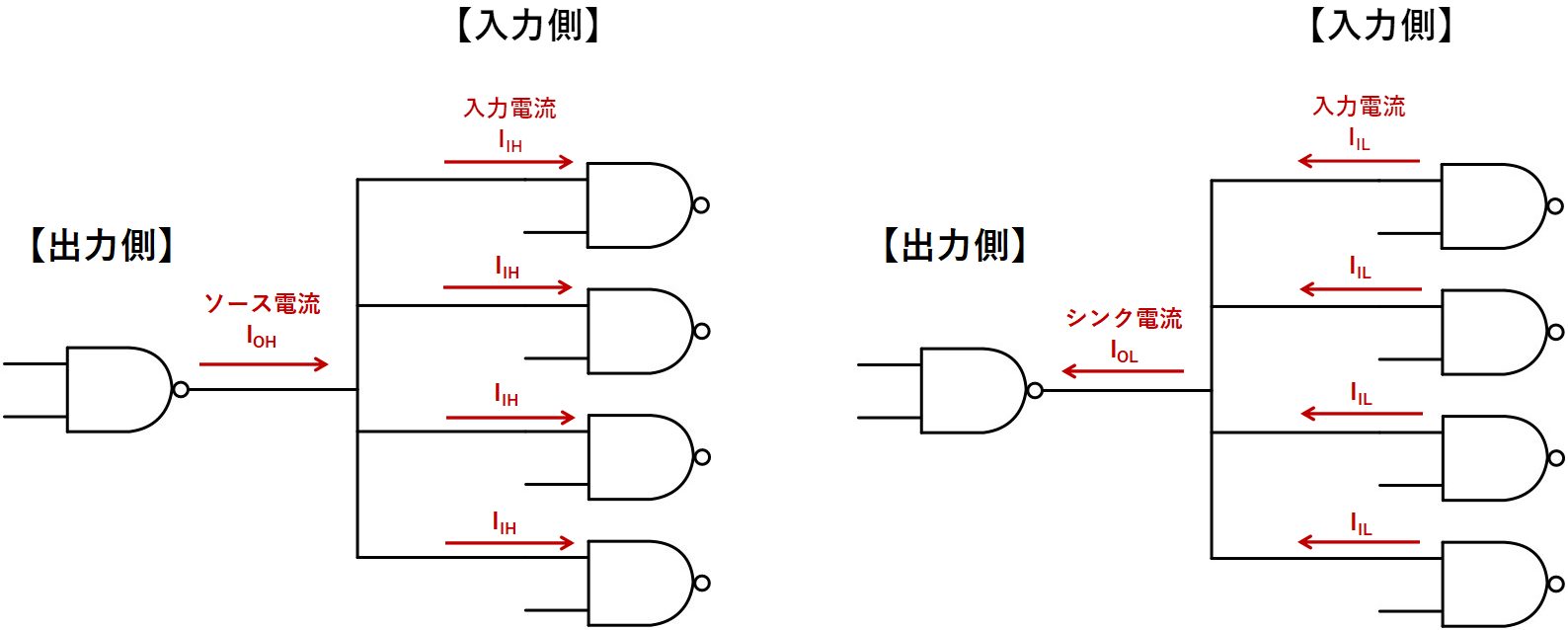

TTLの入力をHi、またはLoにするには出力側から電流を流し込む、または引き込む必要があります。

入力をHiにするために必要な電流はIIH、Loにするために必要な電流はIILとして規定されています。

出力側には最大ソース電流:IOH、最大シンク電流:IOLが規定されています。

ファンアウトは入力電流と出力電流の比で決まり、以下の式で計算できます。

FANOUT = IOH / IIH(出力Hi時)

FANOUT = IOL / IIL(出力Lo時)

IIHが20μA、IOHが1mAであれば、ファンアウトは50と計算することができます。

ファンアウトを超える数の出力回路を接続してしまった場合、出力信号が鈍ってしまったり、減衰したりします。

CMOSのファンアウト

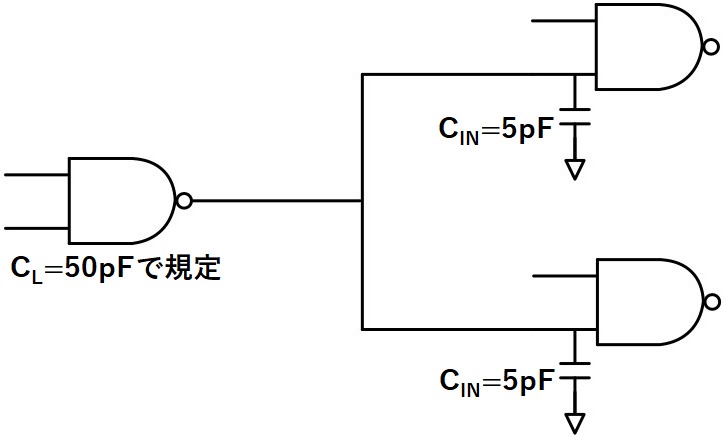

CMOSの場合は入力に電流が流れないため電流能力を考える必要はありませんが、入力側の入力容量による立ち上がり/立ち下がり時間の遅れを考慮する必要があります。

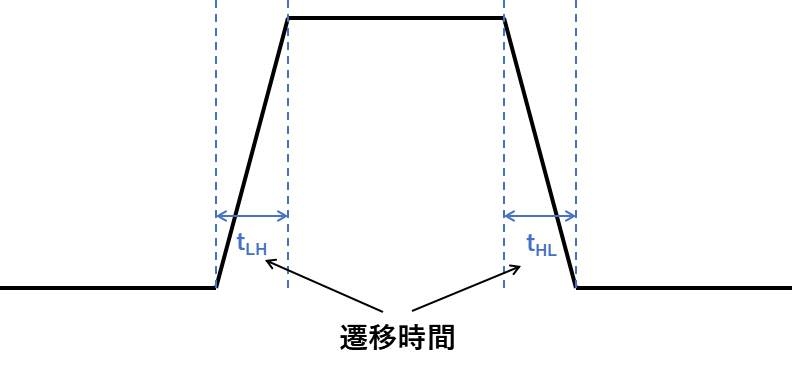

通常、CMOSロジックICには出力遷移時間(Hi⇔Loになるまでの時間)が規定されています。

その条件として出力に接続する負荷容量:CLも規定されています。

つまり、CLを超える容量が入力側に付加されていると、データシートで規定された遷移時間を守れないということになります。

これより、CMOSのファンアウトは入力容量:CINと負荷容量:CLの比で決まり、以下の式で計算できます。

FANOUT = CL / CIN

CINが5pF、CLが50pFであれば、ファンアウトは10となります。