フリップフロップ回路とは?種類とそれぞれの動作をわかりやすく解説

フリップフロップとは、1ビットの情報を保持できる論理回路で、過去の入力によって決まった状態と現在の入力によって出力が決まる順序回路の一つです。

過去の入力情報を保持して記憶することができるため、記憶回路、または記憶素子とも呼ばれます。

ANDやORなどの組み合わせ回路との違いは、組み合わせ回路の場合は情報を保持せず、現在の入力によってのみ出力が決まるという点です。

フリップフロップには以下の4種類があります。

- RSフリップフロップ

- Dフリップフロップ

- JKフリップフロップ

- Tフリップフロップ

それぞれについて動作をわかりやすく説明していきます。

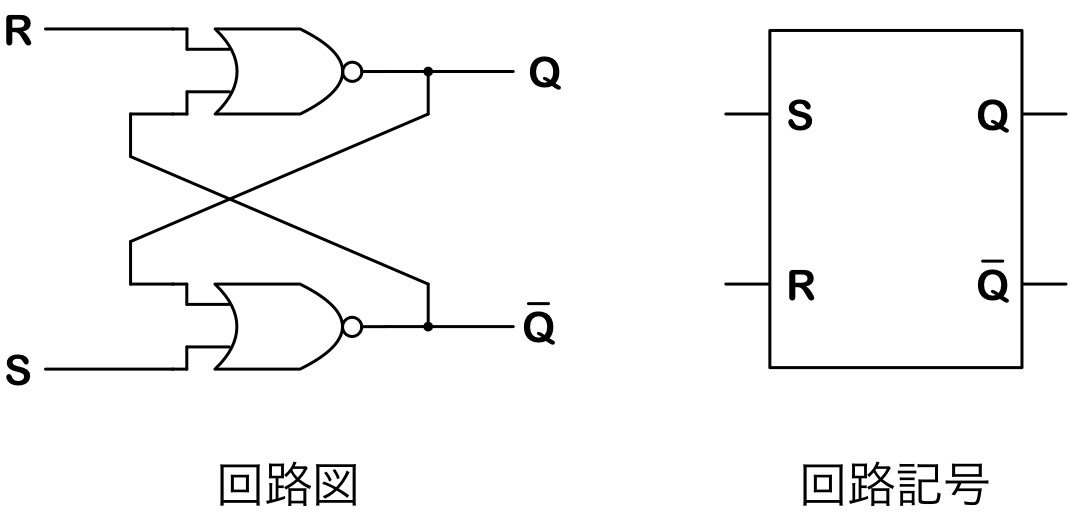

RSフリップフロップ(RS-FF)

RSフリップフロップは、SET端子とRESET端子の2つの入力端子があり、SET端子に一度Hiが入力されるとRESETされるまで出力の状態を保持し続けます。

RSフリップフロップ回路は2つのNORで構成されます。

真理値表とタイムチャートは以下の通りです。

| S | R | Q | Q |

|---|---|---|---|

| 0 | 0 | 保持 | |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 禁止 | |

SET、RESET端子を両方Hi入力にするのは禁止されています。

両方Hiとした場合はQ=Q=0となり不定となるわけではないのですが、その後S=R=0となった場合の出力が安定しません。

SET、RESET端子のどちらが速くLoとなるかで状態が決まり、SET端子の方が遷移が速い場合はQ=0、Q=1となり、逆にRESET端子の遷移が速い場合はQ=1、Q=0となります。

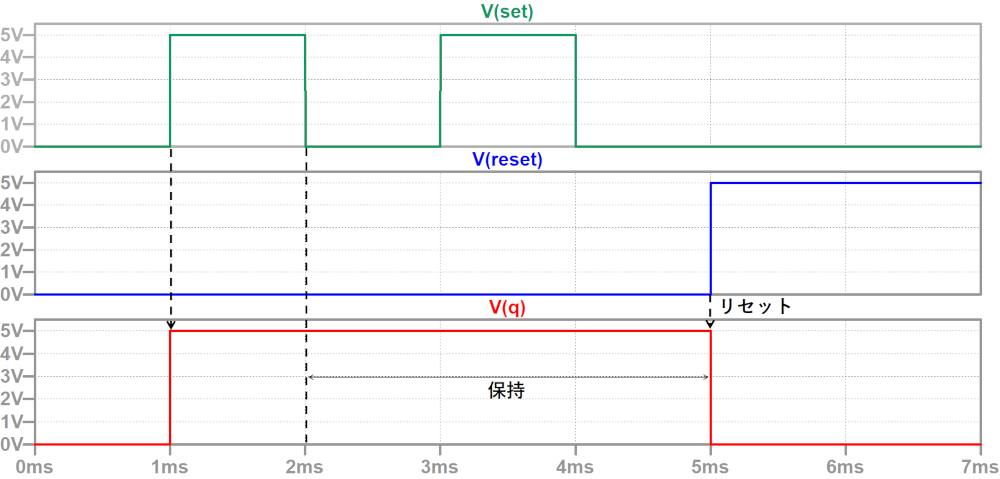

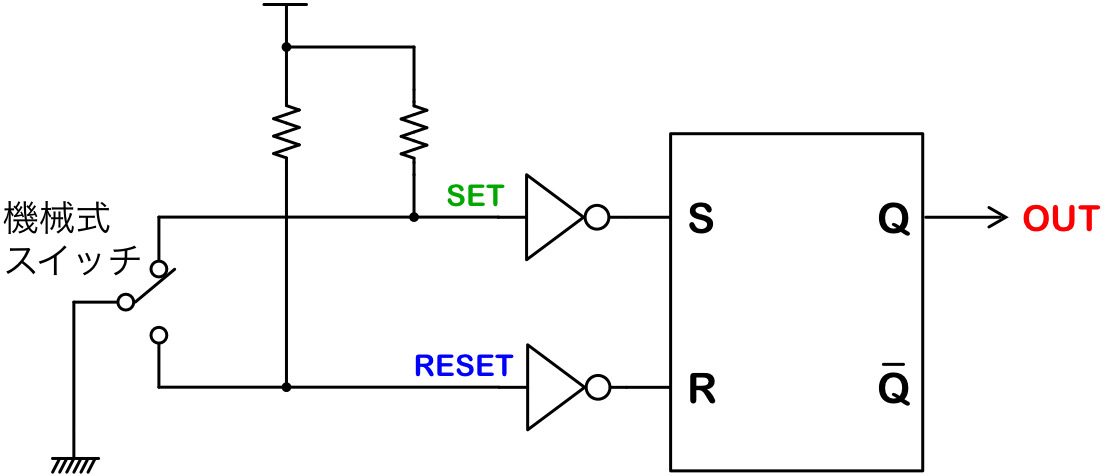

RSフリップフロップの用途

RSフリップフロップは、機械式スイッチなどチャタリングの起こる電気信号の安定化に使われます。

入力端子が一度Hiを検出すれば、チャタリングが起こってLoレベルに下がったとしても、出力を保持し続けることができます。

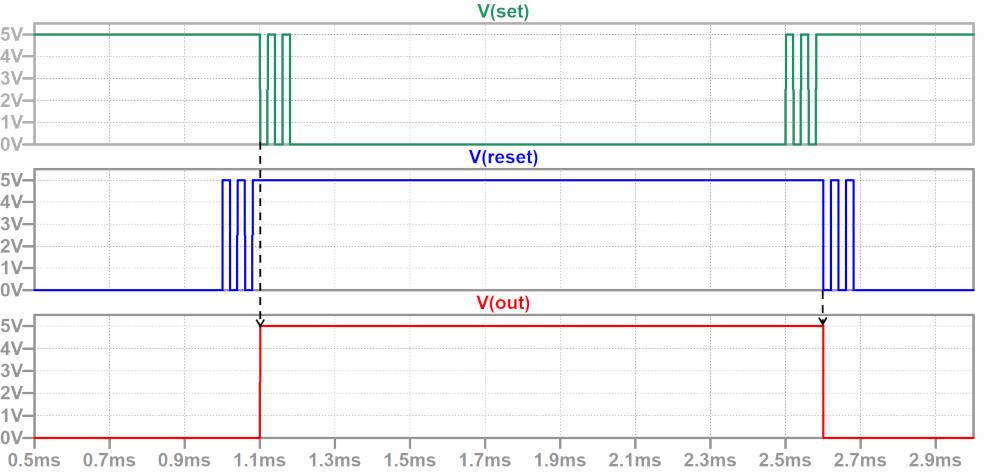

下図がチャタリング対策回路の例です。

この回路の動作のタイムチャートを示します。

セット、リセット共に、最初の遷移だけを捉え、その後のチャタリングによる影響を受けていないことが分かります。

Dフリップフロップ(D-FF)

Dフリップフロップは、データ入力端子(D)とクロック入力端子(CLK)を持ち、CLKがHiの時のDの値を記憶して保持します。

Dフリップフロップの用途はデジタル回路のクロック同期設計です。

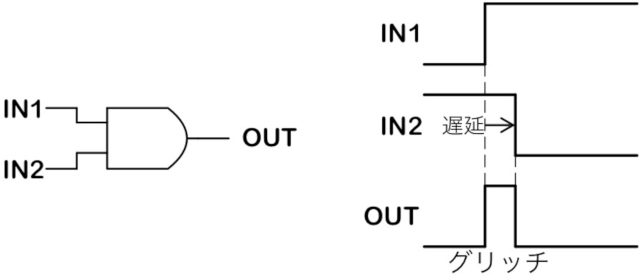

組み合わせ回路や非同期式回路の場合、信号の遅延の差により短い「グリッチ」が発生することがあります。

グリッチは、想定外のタイミングでの異常信号なので、誤動作の原因になります。

クロック同期設計を行うことで安定したタイミングで信号を切替られるため、誤動作を防ぐことができるのです。

Dフリップフロップには2つのタイプがあります。

CLKがHiの期間はDの値を通す「ゲート型」と、CLKの立ち上がりエッジでDの値を取り込む「エッジトリガ型」です。

ゲート型Dフリップフロップ

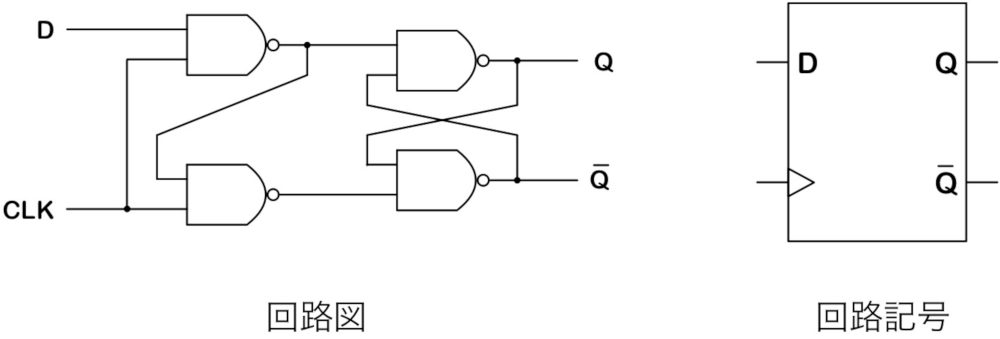

ゲート型は4つのNANDで構成されます。

真理値表は以下の通りです。

| CLK | D | Q | Q |

|---|---|---|---|

| 0 | 0 | 保持 | |

| 0 | 1 | 保持 | |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

CLKがLoの時はDの値の変化を反映させず、前の状態を保持します。

CLKがHiになるとDの値によって出力を更新します。

したがって、CLKに同期してDの値を次段へ伝えることができるのです。

エッジトリガ型Dフリップフロップ

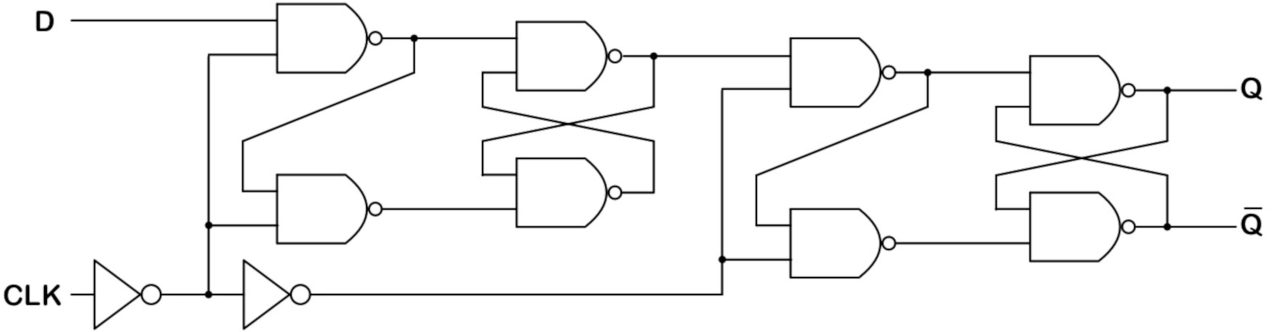

ゲート型に比べると少し複雑な回路になります。

真理値表は以下の通りです。

| CLK | D | Q | Q |

|---|---|---|---|

| 0 | 0 | 保持 | |

| 0 | 1 | 保持 | |

| 1 | 0 | 保持 | |

| 1 | 1 | 保持 | |

| ↑ | 0 | 0 | 1 |

| ↑ | 1 | 1 | 0 |

| ↓ | 0 | 保持 | |

| ↓ | 1 | 保持 | |

「↑」は立ち上がりエッジを、「↓」は立ち下がりエッジを示します。

立ち上がりエッジでのみDの値を取り込み、その他の状態では出力を保持したままになります。

Dフリップフロップの使用例

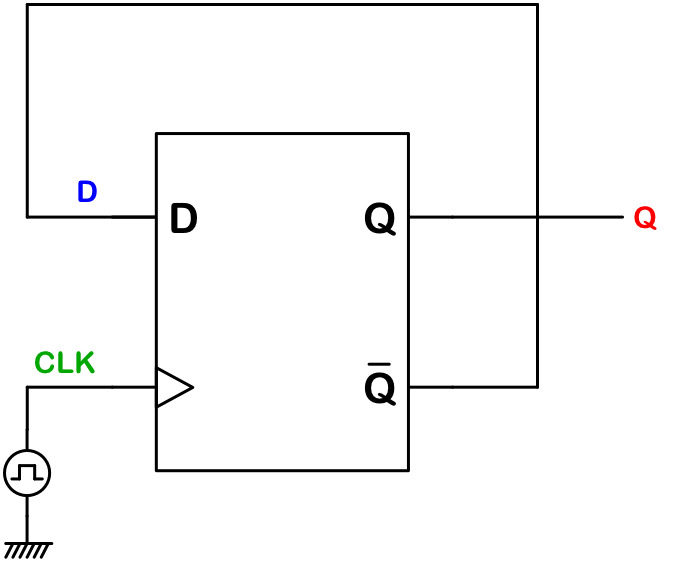

Dフリップフロップの使用例として、分周回路が挙げられます。

分周回路とは、元となるクロック周波数を整数分の一に落とす回路。

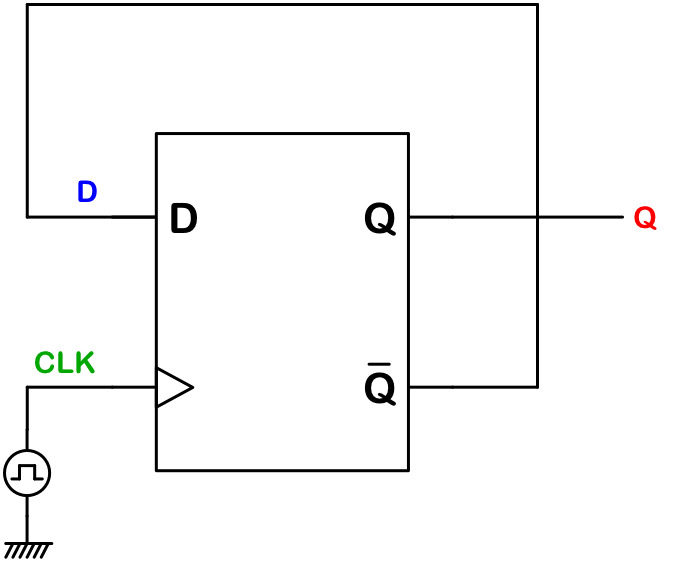

下図はエッジトリガ型を使った、クロックの周波数を1/2にする分周回路です。

QとD端子を接続していますので、CLKのHiエッジのタイミングごとに出力が反転するため、周波数が1/2になります。

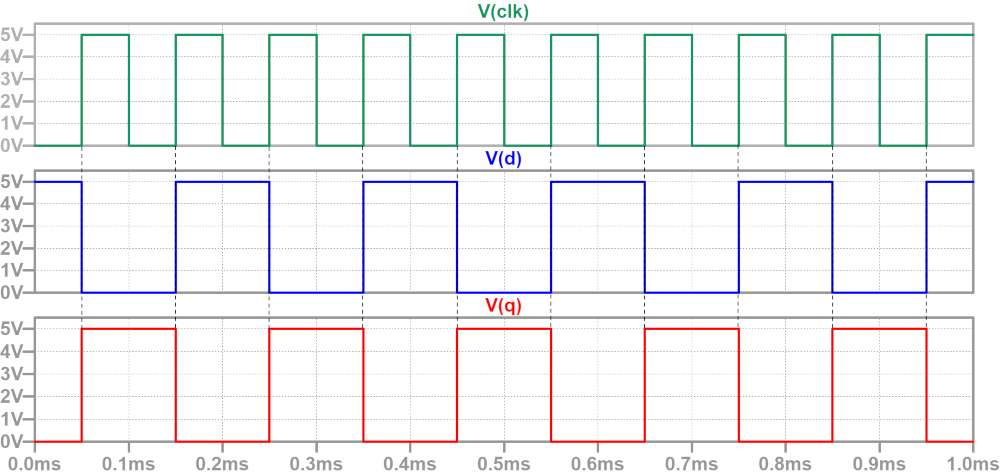

下図が動作波形です。

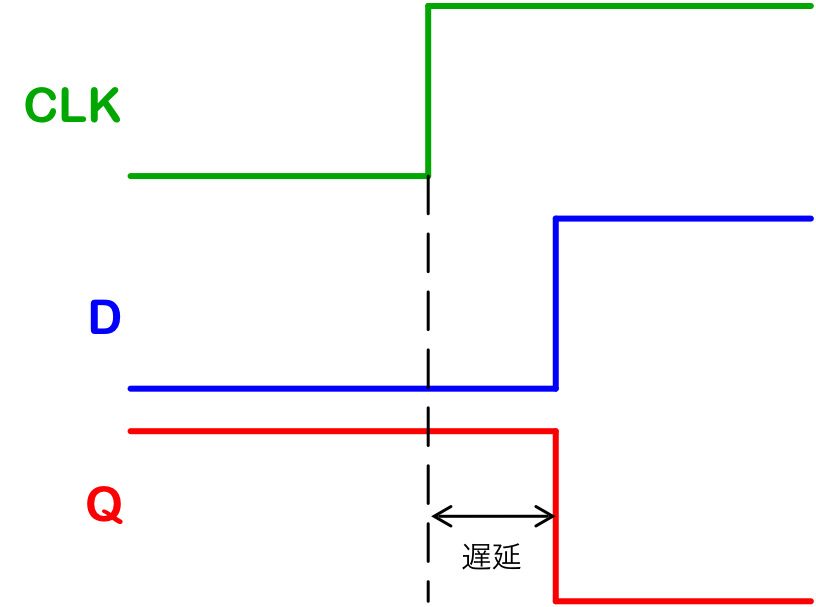

CLKと出力が同時に切り替わっているので分かりにくいのですが、拡大すると下図のようになっています。

CLKの立ち上がりのタイミングでDの値を判定します。

この場合、D=Loとなっていますので、QがHi⇒Loに切り替わります。

同様にQがHiに切り替わりますので、ショートされているDにもHiが入力されます。

エッジトリガなので、DがLoからHiに切り替わっても、次の立ち上がりエッジまでは出力は切り替わらず保持されます。

次の立ち上がりエッジでは、DがHiの状態で判定されますので、QがLo⇒Hiに切り替わります。

つまり、CLKの立ち上がりエッジごとにQがHi⇔Loを切り替わるため、QはCLKの1/2の周波数になるわけです。

また、Qが0⇔1を交互に繰り返すことから、2進カウンタとしても使えます。

JKフリップフロップ(JK-FF)

JKフリップフロップは、RSフリップフロップで禁止されていた(1,1)の入力が許可されたフリップフロップです。

下記の真理値表のように、(1,1)の入力以外はRS-FFと同様で、(1,1)が入力されるとQとQが前の状態から反転します。

| J | K | Q | Q |

|---|---|---|---|

| 0 | 0 | 保持 | |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 反転 | |

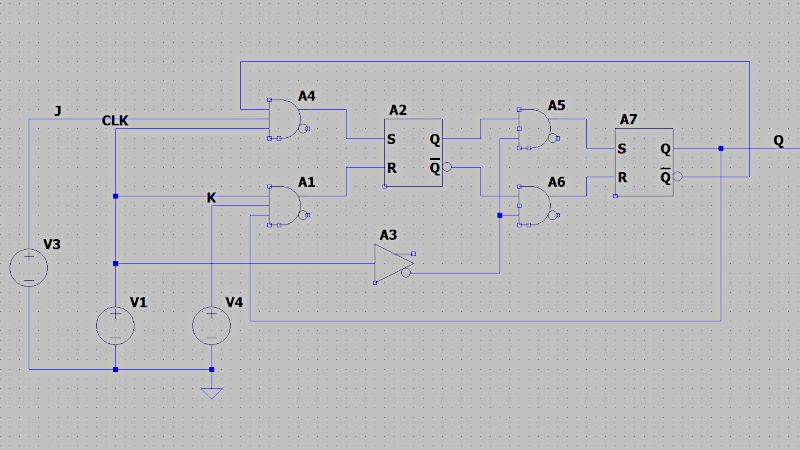

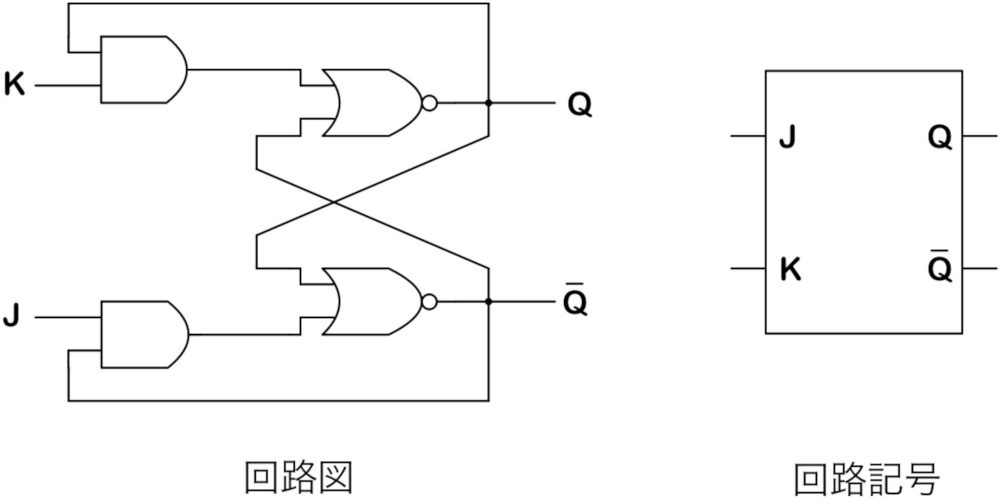

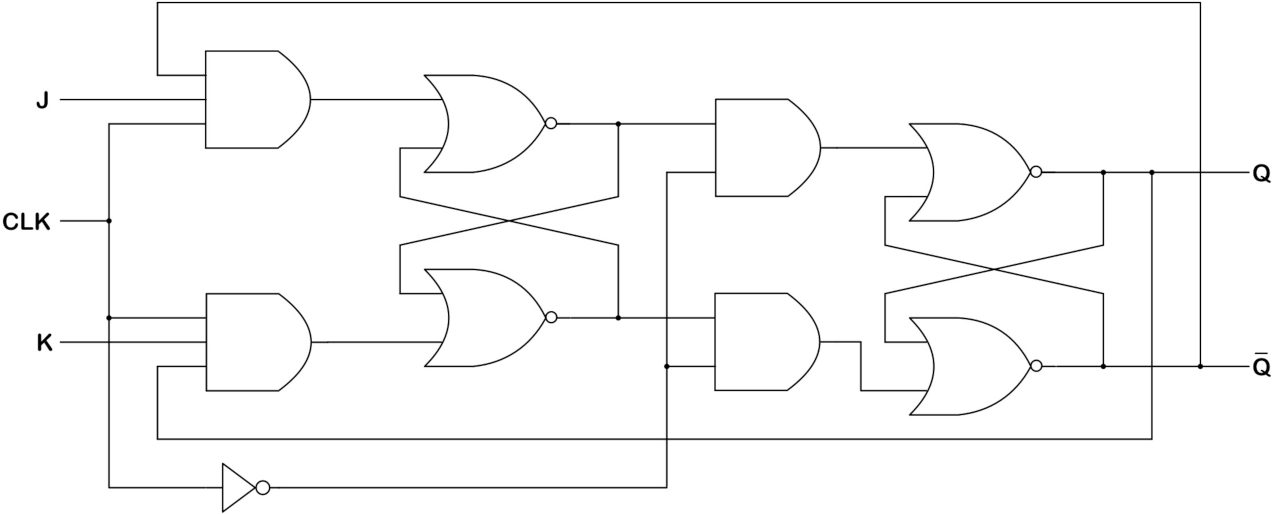

JKフリップフロップの基本的な回路図は下図のようなものです。

しかし、実際に上記回路で(J,K)=(1,1)を入力してシミュレーションを行うと、収束しないか、非常に長いシュミレーション時間を要します。

出力が前の状態から反転するという特性上、(J,K)=(1,1)が入力されている限り、回路の応答速度の限界で反転し続けてしまうためです。

そこで、実際にはエッジトリガ型の同期タイプが使われます。

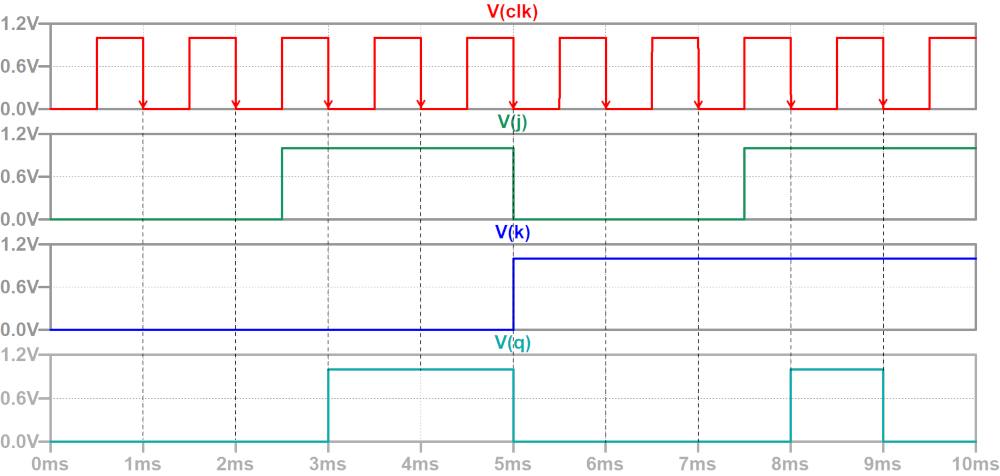

上記回路はネガティブエッジトリガとなっており、タイムチャートは下図のようになります。

(J,K)=(1,1)の入力では、クロックの立ち下がりエッジごとに出力が反転しているのが分かります。

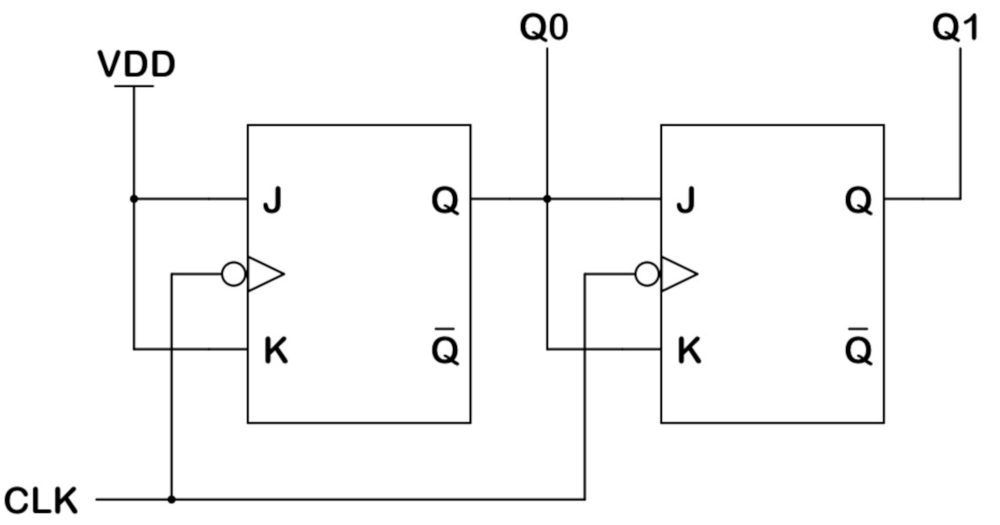

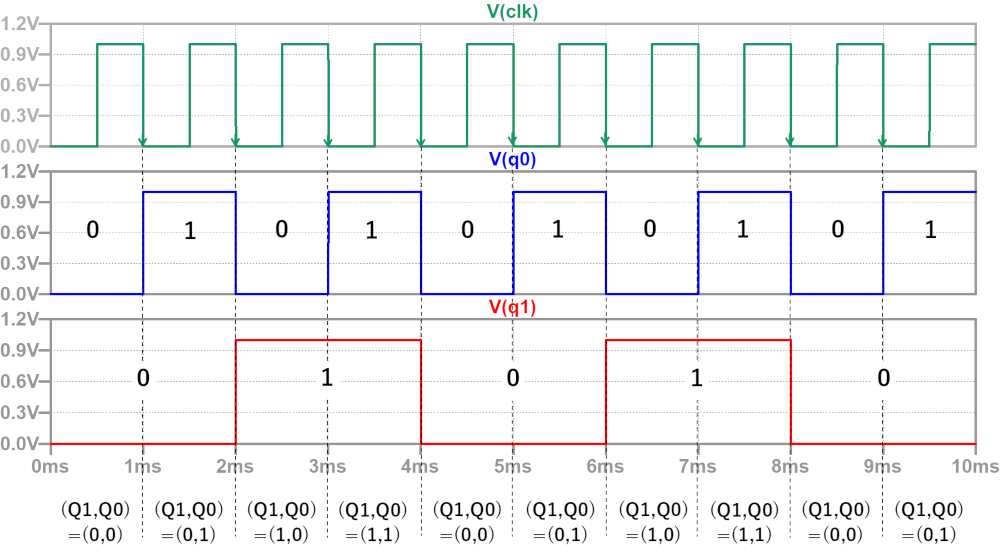

JKフリップフロップを使った4進カウンタ

JKフリップフロップの応用例として、4進カウンタを例に挙げ解説します。

一段目のJKの入力は1なので、クロックの立ち下がりエッジごとに出力が反転します。

二段目のJKの入力は1段目のQが接続されているため、2回に1回(J,K)=(1,1)となります。

したがって、2段目の出力は、1段目の半分の周期で反転することになります。

したがって、(Q1,Q0)は(0,0)⇒(0,1)⇒(1,0)⇒(1,1)と変化していきますので、0~3までをカウントすることができるのです。

Dフリップフロップでも同様に4進カウンタを組むことができます。

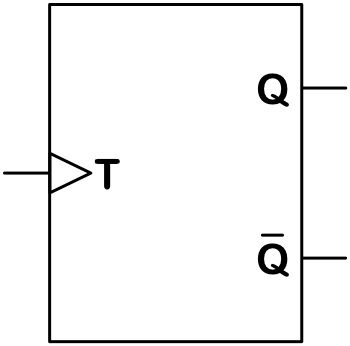

Tフリップフロップ(T-FF)

Tフリップフロップは、Toggle(トグル)フリップフロップの略で、入力TのHiエッジごとに出力が反転します。

Tフリップフロップの回路記号と真理値表は以下の通りです。

| T | Q | Q |

|---|---|---|

| 0 | 保持 | |

| 1 | 保持 | |

| ↑ | 反転 | |

| ↓ | 保持 | |

気づいた方もおられると思いますが、既にTフリップフロップの回路は出てきています。

Tフリップフロップの回路

既に2つの方法でTフリップフロップの回路を解説していますが、改めてご紹介しましょう。

Dフリップフロップを使った回路

エッジトリガ型のDフリップフロップでTフリップフロップが実現できます。

分周回路として紹介したこちらの回路です。

CLK端子がT端子に相当します。

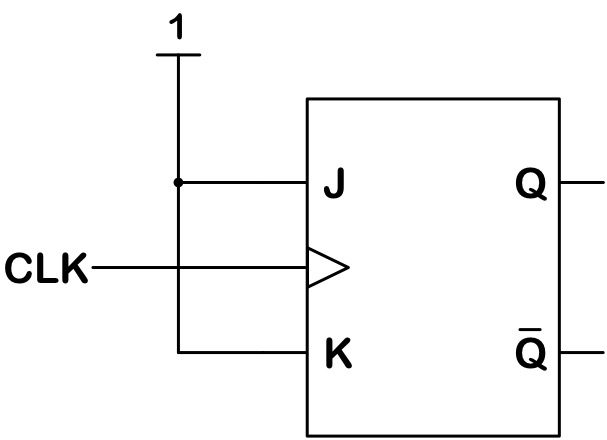

JKフリップフロップを使った回路

JKフリップフロップの2つの入力を1に固定することでも、Tフリップフロップが実現できます。

こちらもCLK端子がT端子に相当します。