CMOSレベルとは?TTLレベルとの違い

CMOSレベルとは、一般的なCMOSロジックICの入出力条件です。

TTLレベルと違い、電源電圧:VDDに依存します。

CMOSレベルの規格

CMOSレベルの一般的な規格は下記のようになります。

| Hiレベル入力電圧 | 0.7×VDD |

|---|---|

| Loレベル入力電圧 | 0.2×VDD |

| Hiレベル出力電圧 | VDD-0.8V |

| Loレベル出力電圧 | 0.4V |

VDDはCMOSロジックICの電源電圧です。

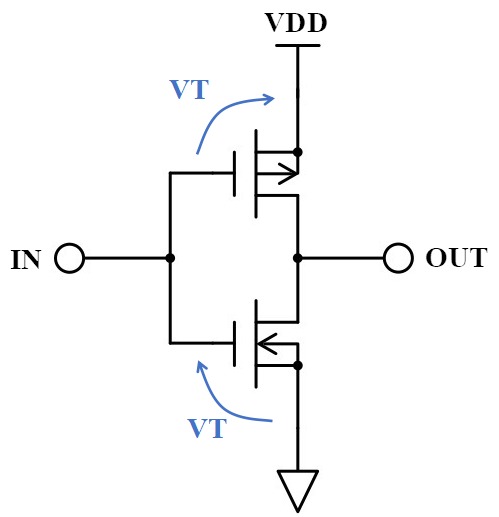

最も基本的なCMOSのインバータ回路を考えます。

VTはCMOSのオン閾値です。

入力がHi(出力がLo)を確定する電圧が「Hiレベル入力電圧」で、入力Lo(出力Hi)を確定する電圧が「Loレベル入力電圧」です。

その間の電圧では「不定」とされ、Hi判定されるかもしれないし、Lo判定されるかもしれない領域です。

出力電圧はCMOSのオン抵抗による電圧ドロップの最大値で決まっています。

Hiレベルの方が低下幅が大きいのは、同じサイズであればPMOSの方がオン抵抗が大きくなるためです。

TTLレベルとの違い

TTLレベルは、バイポーラトランジスタで構成されたロジックICの入出力規格値です。

CMOSレベルとの違いをまとめると以下のようになります。

| 項目 | CMOSレベル | TTLレベル |

|---|---|---|

| Hiレベル入力電圧 | 0.7×VDD以上 | 2.0V以上 |

| Loレベル入力電圧 | 0.2×VDD以下 | 0.8V以下 |

| Hiレベル出力電圧 | VDD-0.8V以上 | 2.4V以上 |

| Loレベル出力電圧 | 0.4V以下 | 0.4V以下 |