昇降圧DCDCコンバータの動作原理と回路設計方法

昇降圧コンバータ(バックブーストコンバータ)とは、昇圧動作と降圧動作を自動的に切り替え、入力電圧に依らず一定の電圧を出力する回路方式です。

入力電圧の変動幅が大きいバッテリなどを入力電源とする場合に使用されることが多くなります。

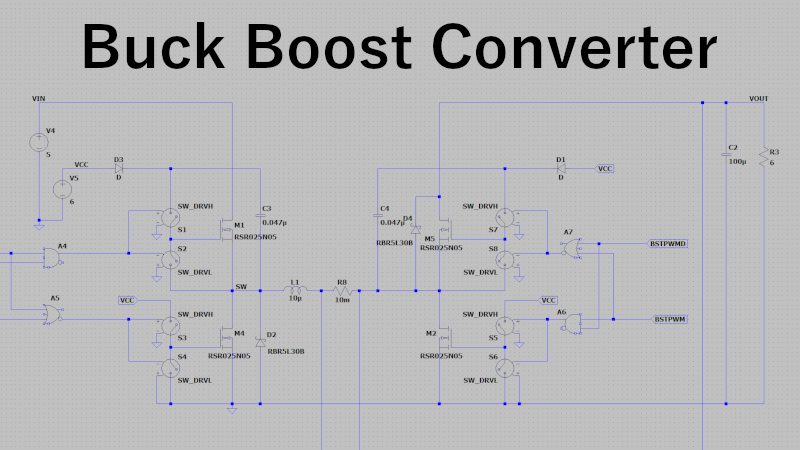

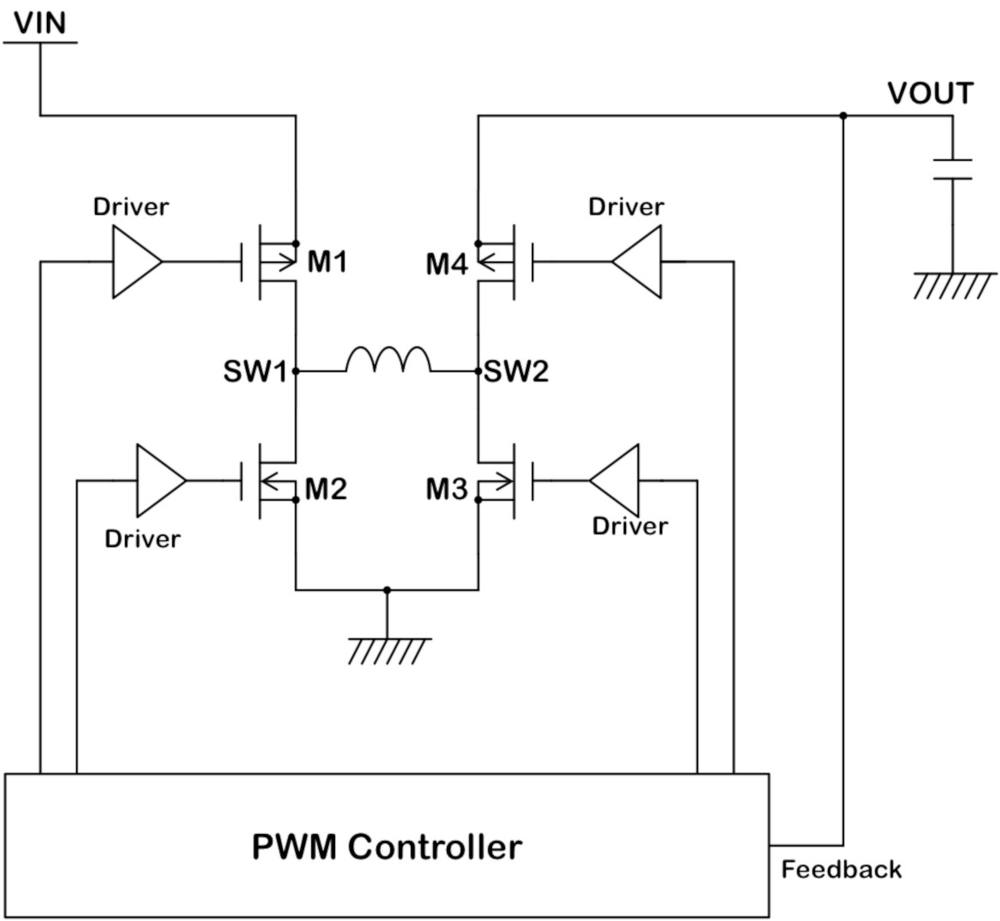

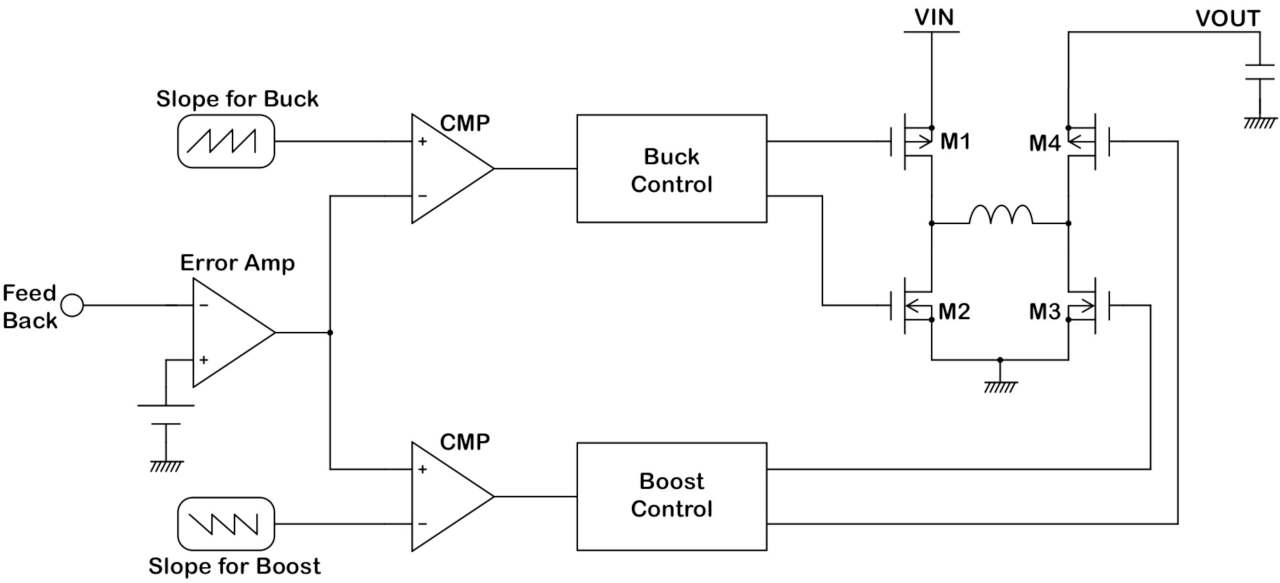

昇圧コンバータの方式には複数ありますが、本稿ではFETを4つ使ったHブリッジ型の昇降圧DCDCコンバータの動作について解説していきます。

Hブリッジ型昇降圧コンバータの基礎

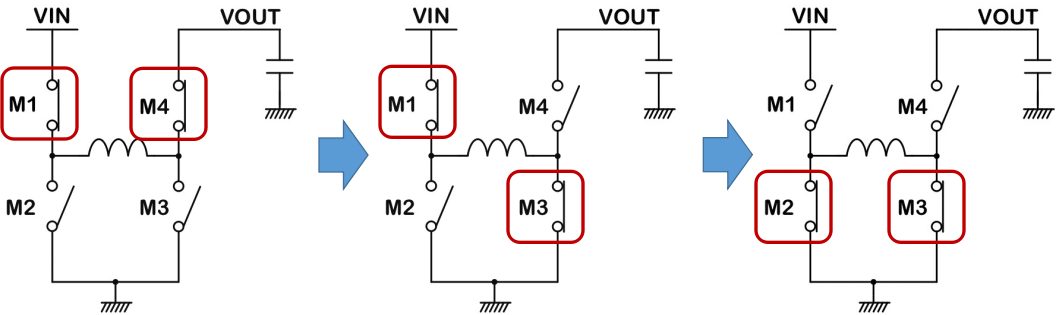

Hブリッジ型昇降圧DCDCコンバータは、MOSFETを4つ使用して、下図のように構成されます。

入力電圧と出力電圧の関係によって、昇降圧電源は3つの動作モードを自動で切り替えます。

降圧モード

入力電圧が出力電圧より十分高い場合は、M1とM2を制御して降圧モードで動作します。

このとき、M3はオフ、M4はオン固定となります。

昇降圧モード

入力電圧≒出力電圧の場合は、4つのFETが全て動作する昇降圧モードで動作します。

昇降圧モードが降圧モードと昇圧モードの間をつなぎ、シームレスに動作が切り替わります。

初期の昇降圧電源は、この昇降圧モードがなかったために、入力電圧≒出力電圧の領域で動作が不安定となり、出力電圧の変動が大きくなってしまっていました。

昇圧モード

入力電圧が出力電圧より十分低い場合は、M3とM4を制御して昇圧モードで動作します。

このとき、M1はオン、M2はオフ固定となります。

PWM制御部の動作原理

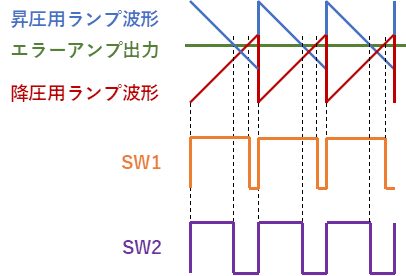

昇降圧電源では、PWM制御をするためのランプ波形(ノコギリ波)が2つ必要になります。

降圧用をアップスロープのノコギリ波、昇圧用をダウンスロープのノコギリ波とします。

そして、それぞれの頂点が重なるようにします。

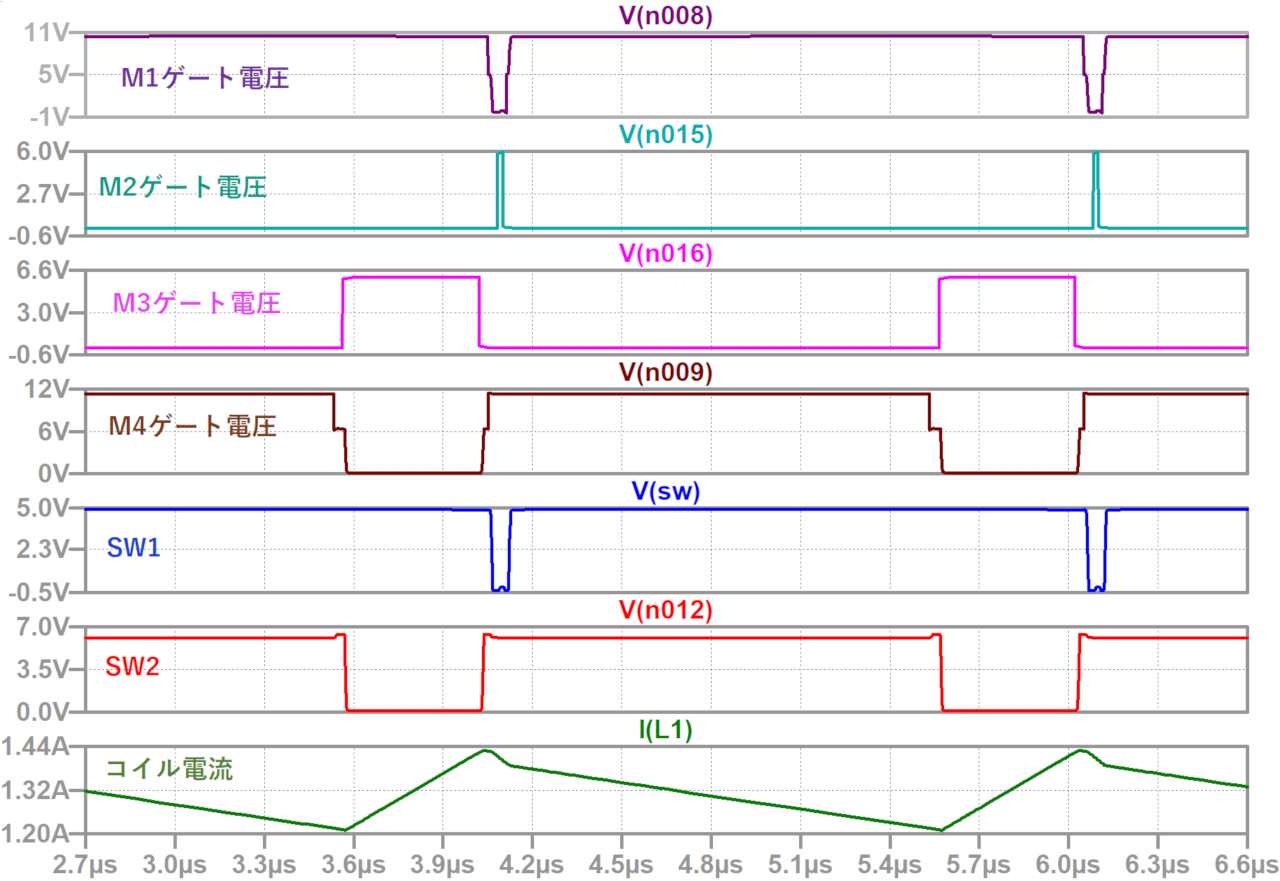

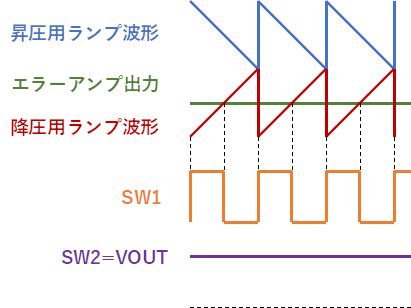

上図は降圧モード時の動作波形です。

通常の降圧DCDCコンバータの動作と同様で、M1がオンのタイミングでスロープが上昇し、エラーアンプ出力を超えるとM1がオフ、M2がオンします。

このとき、昇圧用のノコギリ波よりエラーアンプ出力が低いため、昇圧回路は常にオフ状態(M3がオフでM4がオン)となり、SW2電圧はVOUTと等しくなります。

入力電圧が下がるにつれてエラーアンプの出力が上昇し、降圧動作のオンDUTYが大きくなります。

そしてVIN<VOUTとなると、エラーアンプの出力が降圧モードのノコギリ波のピークを超え、100%オン状態となります。

同時に、昇圧モードのノコギリ波の電圧範囲内に入るため、昇圧動作に切り替わります。

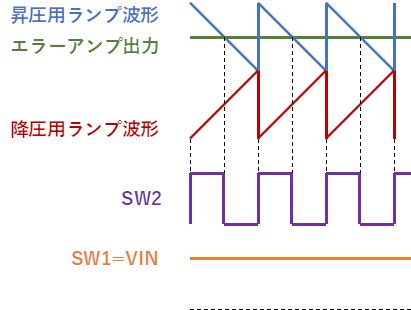

M4がオンのタイミングでスロープが降下し始め、エラーアンプ出力以下となるとM4がオフしM3がオンします。

このとき、降圧用のノコギリ波よりエラーアンプ出力が高いため、降圧回路は常にオン状態(M1がオンでM2がオフ)となり。SW1電圧はVINと等しくなります。

ここまでが昇降圧電源動作の基本的な制御の考え方ですが、前述の問題があります。

昇圧と降圧のノコギリ波のピークをぴったり合わせていると、ばらつきによりずれた場合にモードが不定となる領域が発生し、降圧⇔昇圧のモード切り替えがシームレスに繋がらないのです。

そこで、昇圧と降圧のノコギリ波を少しオーバーラップさせます。

VIN≒VOUT付近で降圧動作と昇圧動作が混在する昇降圧モードで動作します。

M1、M4がオンのタイミングでそれぞれのスロープが上昇・下降します。

昇圧スロープのピークがエラーアンプ出力を下回ると、M4がオフしM3がオンします。

次に降圧スロープがエラーアンプ出力を上回ると、M1がオフし、M2がオンします。

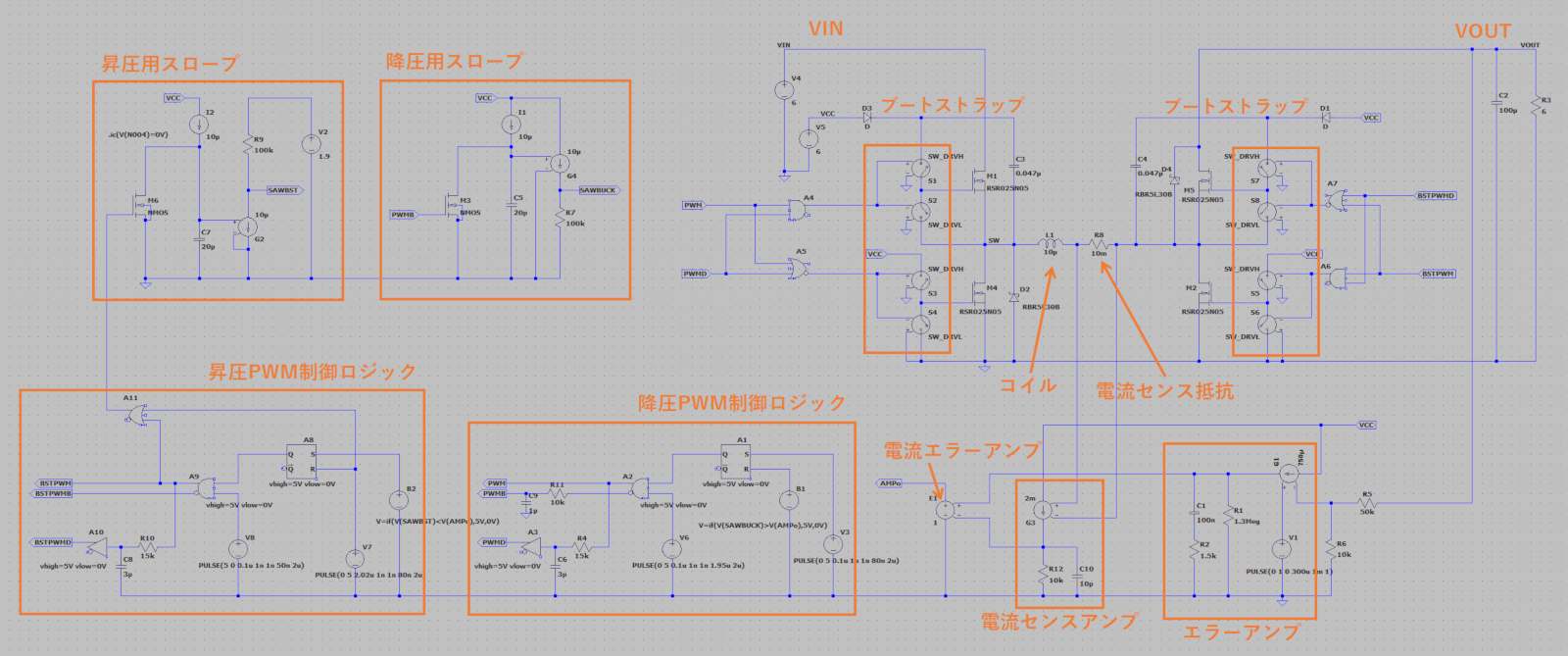

昇降圧DCDCコンバータの内部回路

昇降圧DCDCコンバータの内部回路は下図のようになります。

画像をクリックすると拡大できます

制御方式は平均電流モードを採用しています。

スイッチングMOSFETは全てNchを使用しているので、ブートストラップ回路が追加しています。

LTspiceのシミュレーション回路は下記よりダウンロードして頂けます。

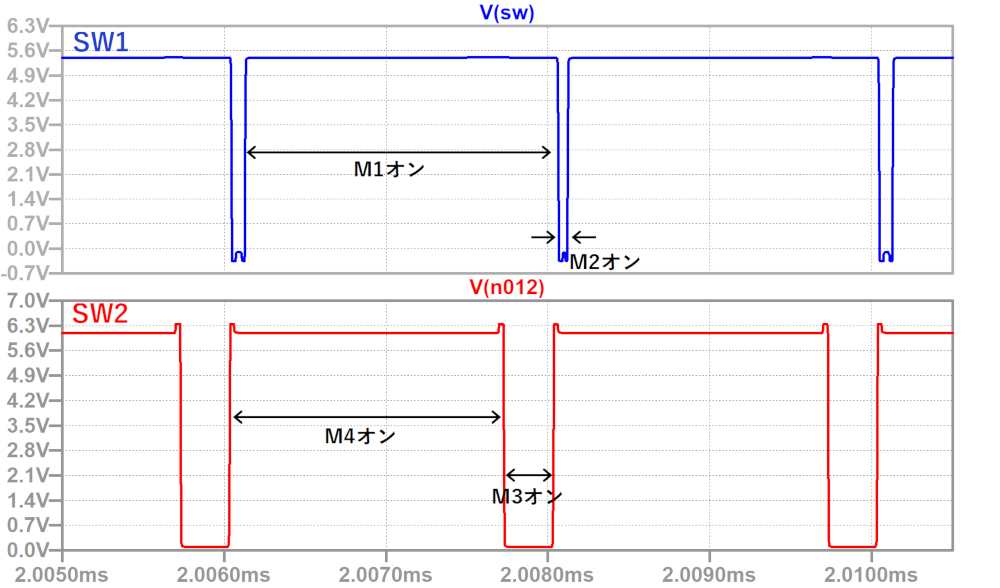

上記回路で昇降圧モード時の動作をシュミレーションすると以下のようになります。